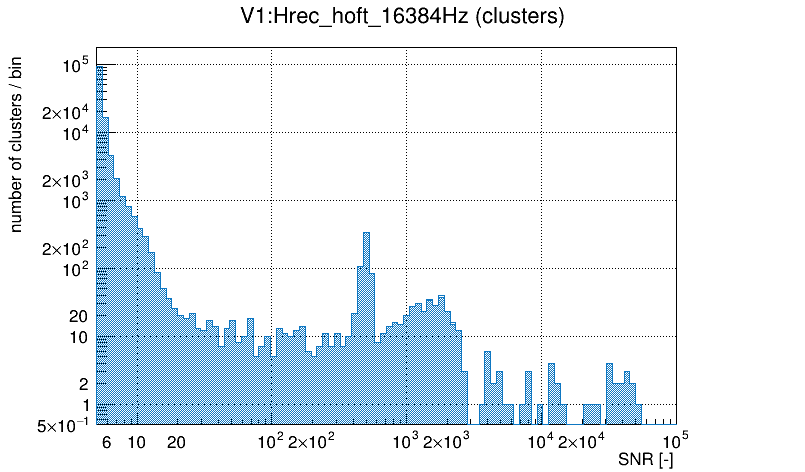

| V1:Hrec_hoft_16384Hz: 122170 clusters |

|---|

| V0 → V1:Sa_PR_F0_Z_CORR_500Hz_0, vetoed clusters: 158 (0.129 %) |

| V1 → V1:Sa_PR_F0_COIL_H3_500Hz_0, vetoed clusters: 150 (0.123 %) |

| V2 → V1:Sa_PR_F0_COIL_H2_500Hz_0, vetoed clusters: 146 (0.120 %) |

| V3 → V1:Sa_PR_F0_COIL_H1_500Hz_0, vetoed clusters: 52 (0.043 %) |

| V4 → V1:Sa_PR_F0_Z_GIPC_500Hz_0, vetoed clusters: 51 (0.042 %) |

| V5 → V1:Sa_PR_F0_ACC_H1_500Hz_0, vetoed clusters: 51 (0.042 %) |

| V6 → V1:Sa_PR_F0_ACC_H3_500Hz_0, vetoed clusters: 47 (0.038 %) |

| V7 → V1:Sa_PR_F0_ACC_V1_FB_500Hz_0, vetoed clusters: 46 (0.038 %) |

| V8 → V1:Sa_PR_Acc1ABS_500Hz_0, vetoed clusters: 45 (0.037 %) |

| V9 → V1:Sa_PR_F0_ACC_V2_FB_500Hz_0, vetoed clusters: 44 (0.036 %) |