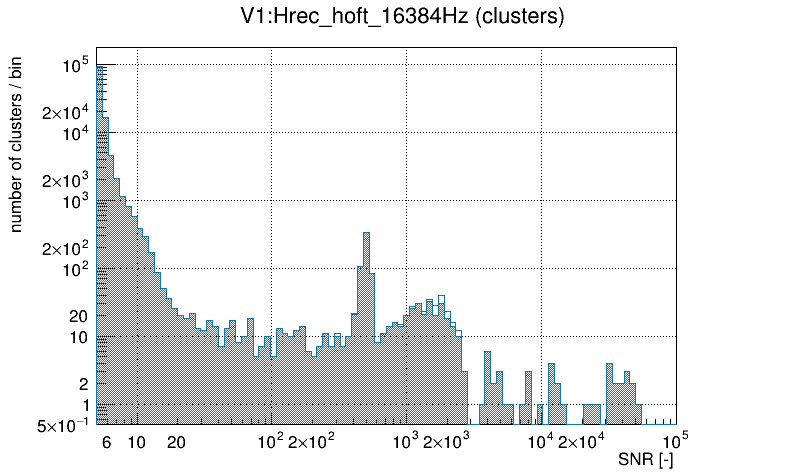

| V1:Hrec_hoft_16384Hz: 122170 clusters |

|---|

| V0 → V1:SPRB_B4_PD2_Audio_0, vetoed clusters: 177 (0.145 %) |

| V1 → V1:SPRB_B4_PD2_Blended_0, vetoed clusters: 174 (0.142 %) |

| V2 → V1:SPRB_B4_PD2_Blended_D_0, vetoed clusters: 173 (0.142 %) |

| V3 → V1:SPRB_B4_QD1_12MHz_Sum_0, vetoed clusters: 124 (0.101 %) |

| V4 → V1:SPRB_B4_QD2_12MHz_Sum_0, vetoed clusters: 116 (0.095 %) |

| V5 → V1:SPRB_B4_QD1_50MHz_SUM_Q_0, vetoed clusters: 101 (0.083 %) |

| V6 → V1:SPRB_B4_PD2_DC_0, vetoed clusters: 97 (0.079 %) |

| V7 → V1:SPRB_B4_QD2_50MHz_SUM_Q_0, vetoed clusters: 92 (0.075 %) |

| V8 → V1:SPRB_B4_QD2_6MHz_H_I_0, vetoed clusters: 83 (0.068 %) |

| V9 → V1:SPRB_B4_QD2_56MHz_H_I_0, vetoed clusters: 78 (0.064 %) |