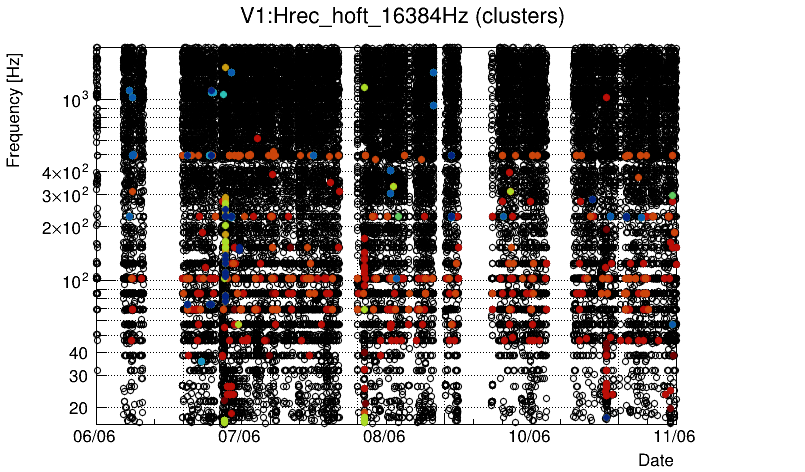

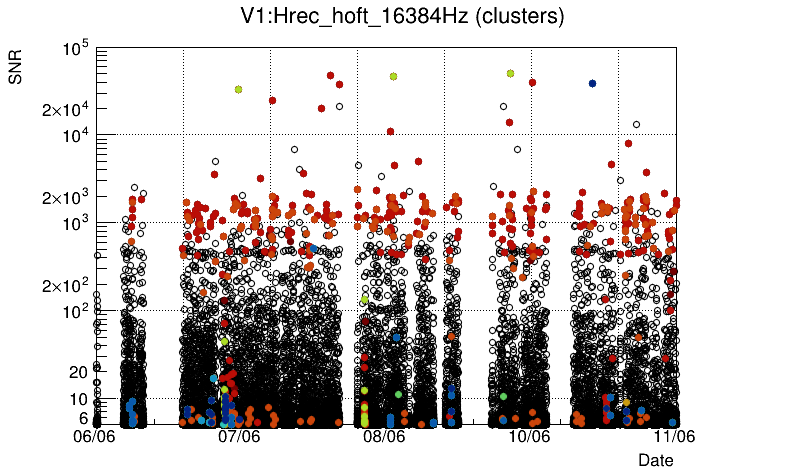

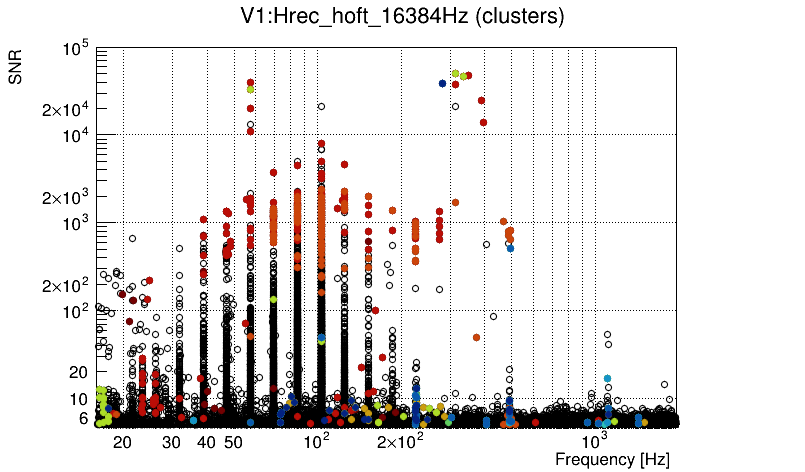

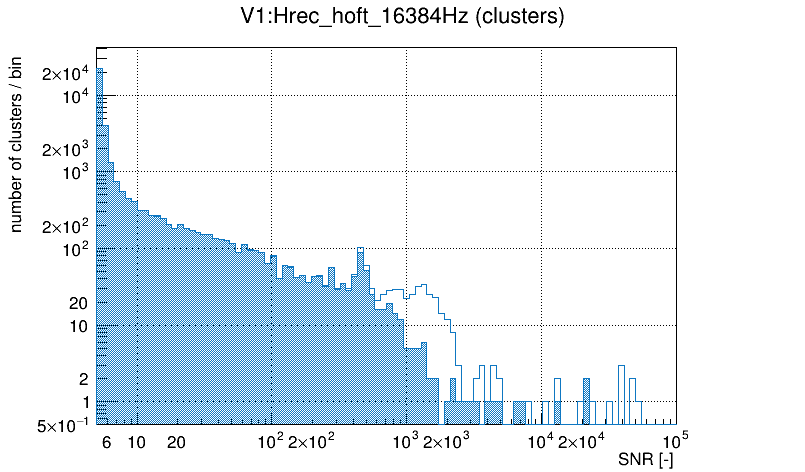

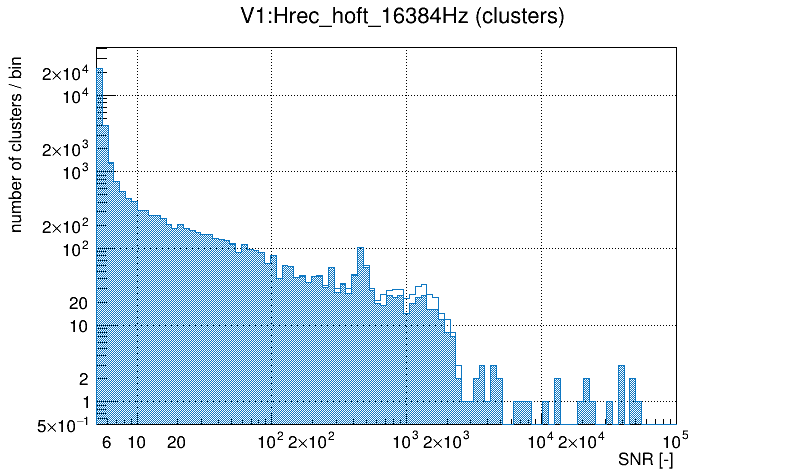

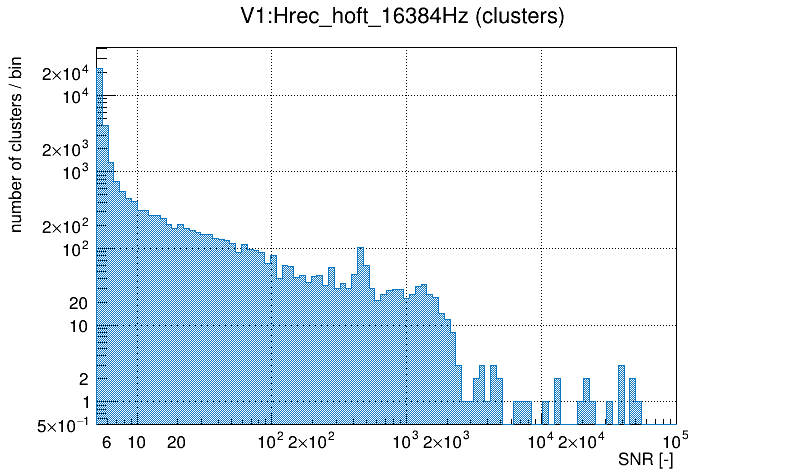

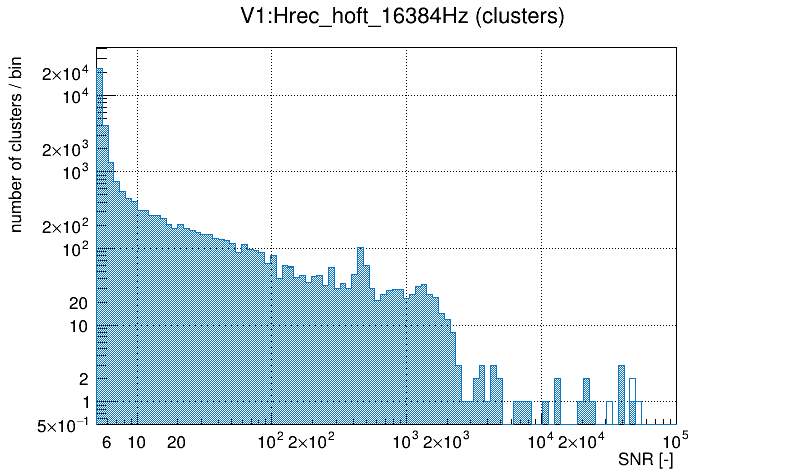

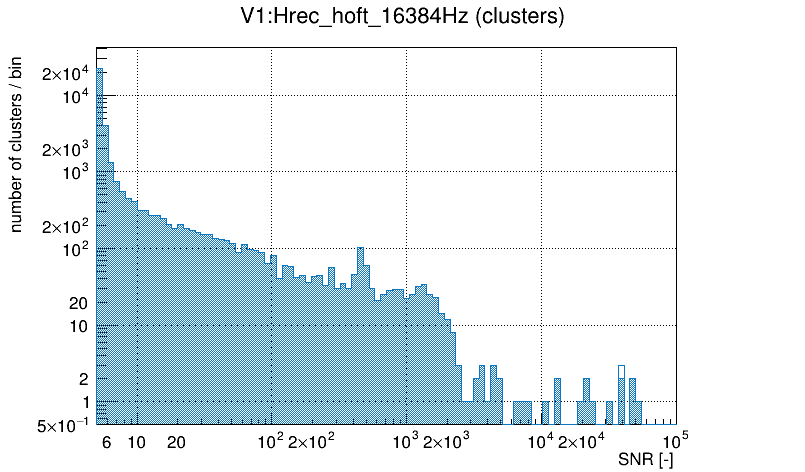

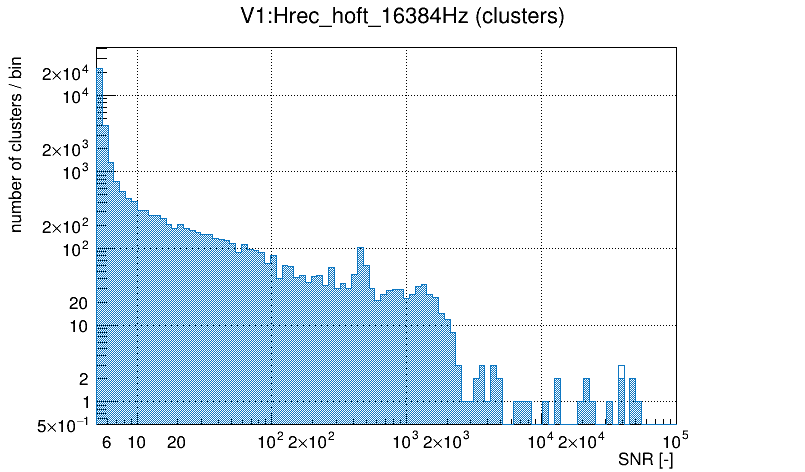

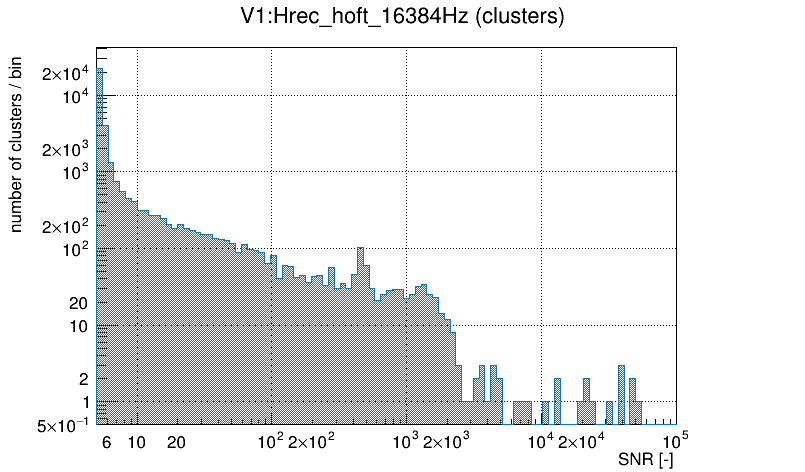

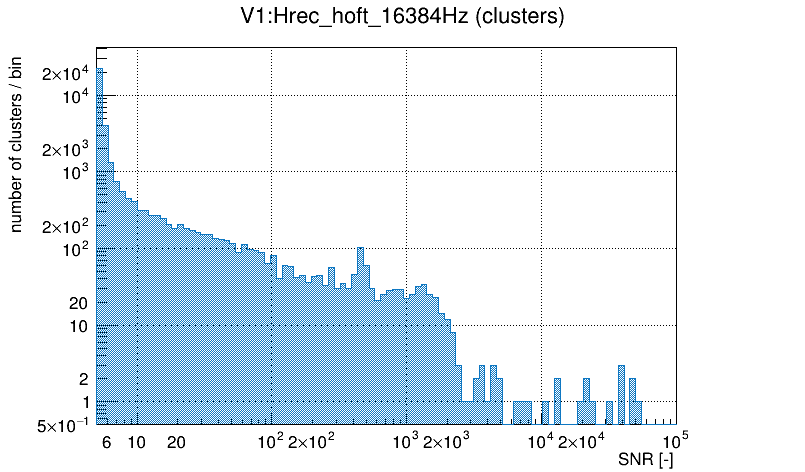

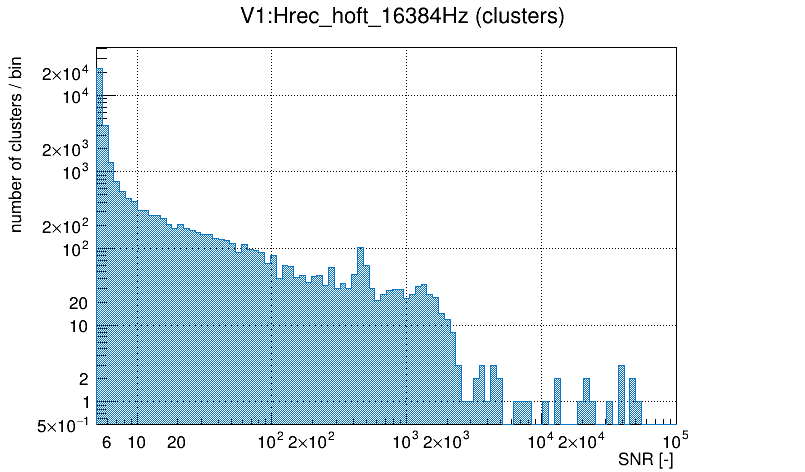

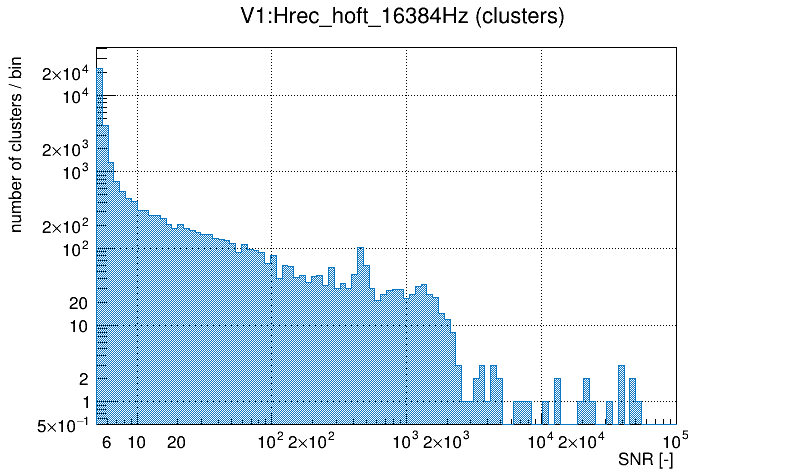

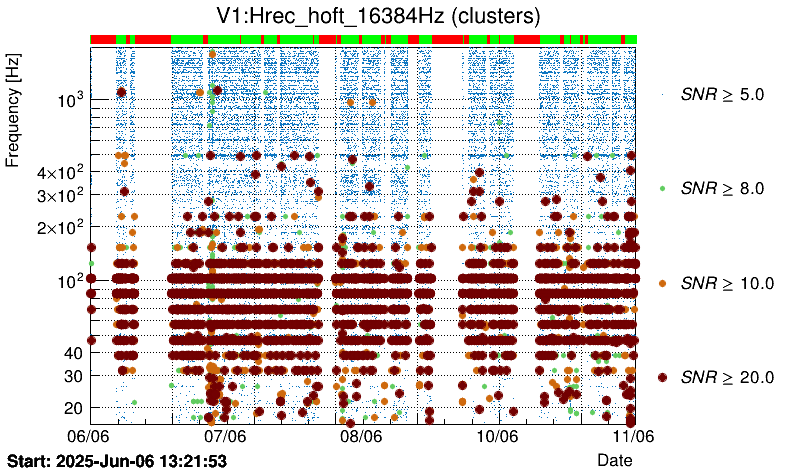

| V1:Hrec_hoft_16384Hz: 34915 clusters |

|---|

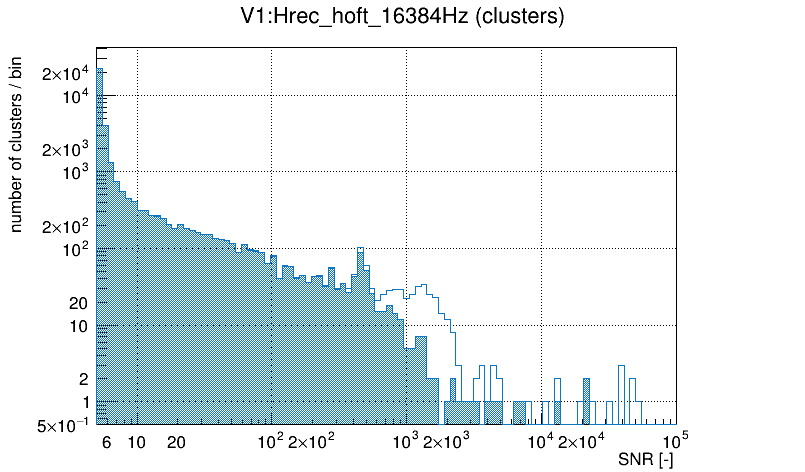

| V0 → V1:SDB2_CAL_B1p_PD1_Audio_10kHz_0, vetoed clusters: 326 (0.934 %) |

| V1 → V1:SDB2_CAL_B1p_PD1_Blended_10kHz_0, vetoed clusters: 325 (0.931 %) |

| V2 → V1:SDB2_POWERSUPPLY_DBOX_LEFT_DOWN_p12V_0, vetoed clusters: 159 (0.455 %) |

| V3 → V1:SDB2_B5_QD2_50MHz_H_Q_0, vetoed clusters: 42 (0.120 %) |

| V4 → V1:SDB2_B5_QD2_6MHz_SUM_Q_0, vetoed clusters: 41 (0.117 %) |

| V5 → V1:SDB2_B5_QD2_112MHz_V_norm_0, vetoed clusters: 37 (0.106 %) |

| V6 → V1:SDB2_B5_QD2_112MHz_Sum_0, vetoed clusters: 35 (0.100 %) |

| V7 → V1:SDB2_B5_QD2_112MHz_V_0, vetoed clusters: 35 (0.100 %) |

| V8 → V1:SDB2_B5_QD2_112MHz_H_norm_0, vetoed clusters: 30 (0.086 %) |

| V9 → V1:SDB2_B5_QD2_56MHz_H_Q_0, vetoed clusters: 26 (0.074 %) |