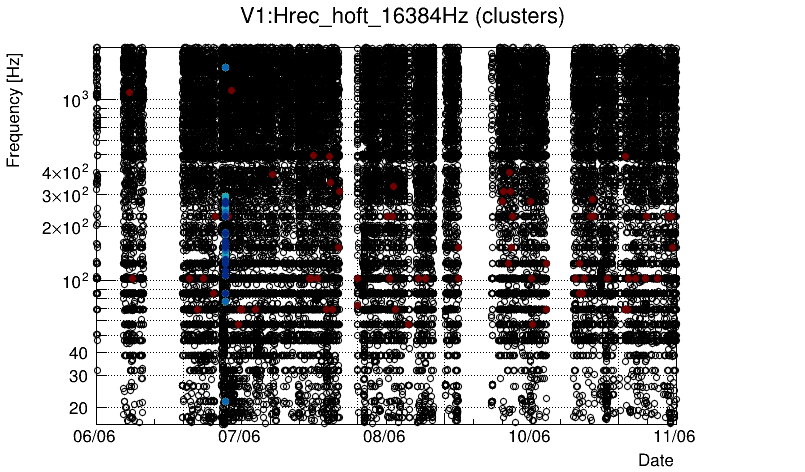

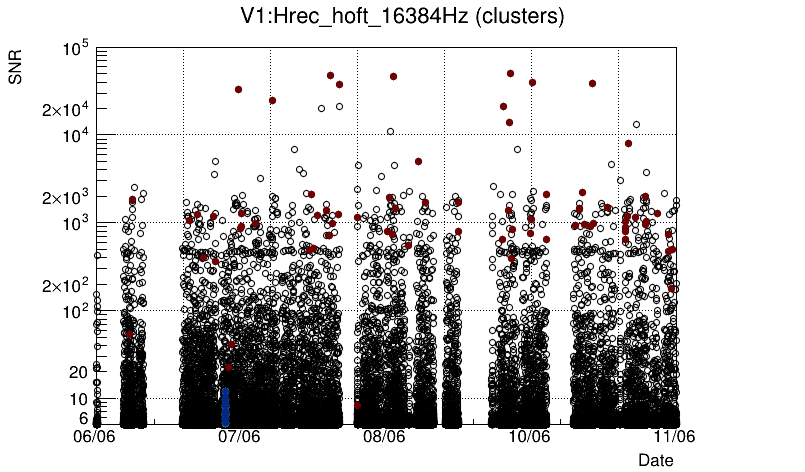

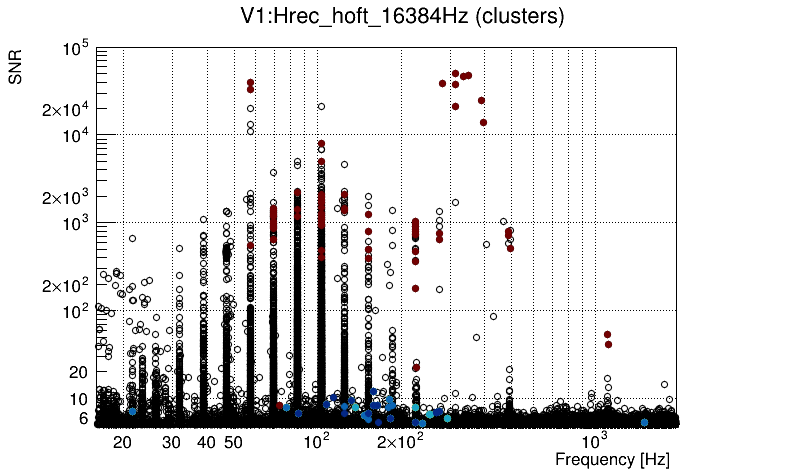

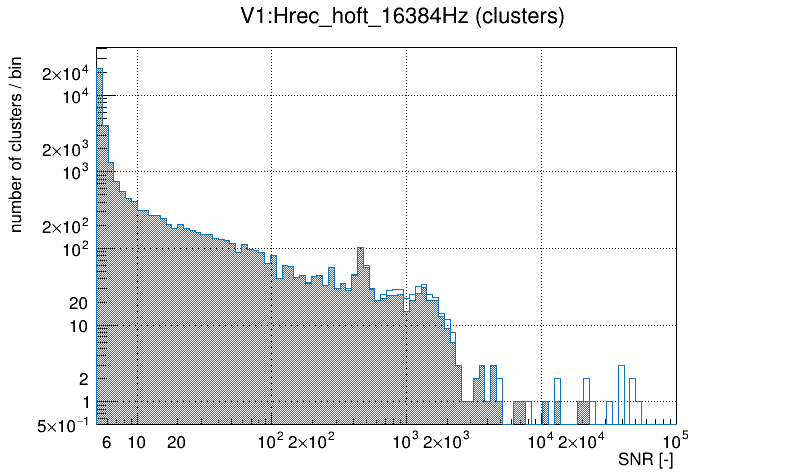

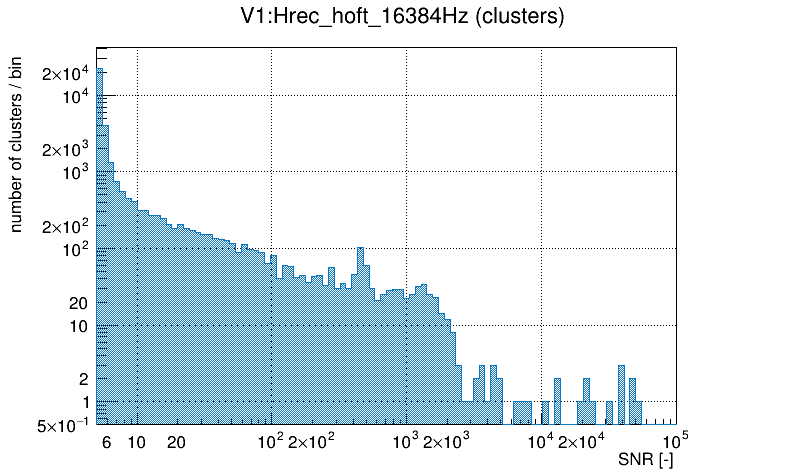

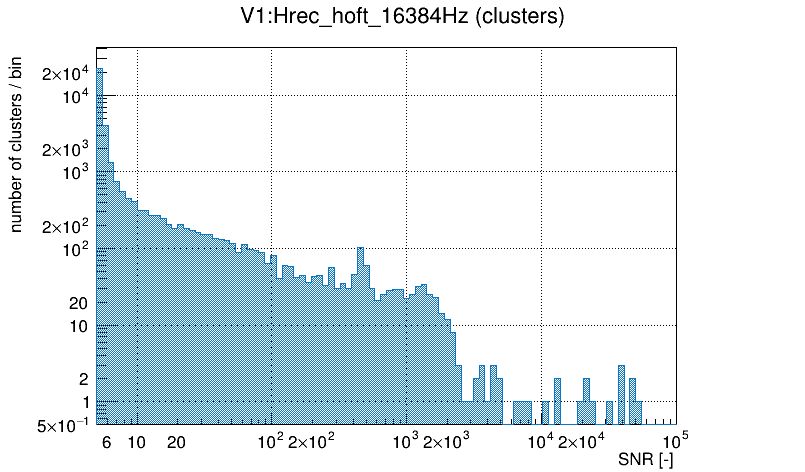

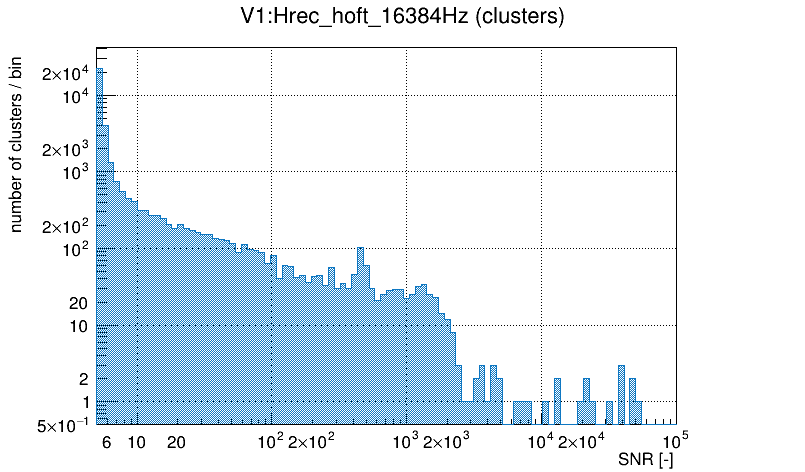

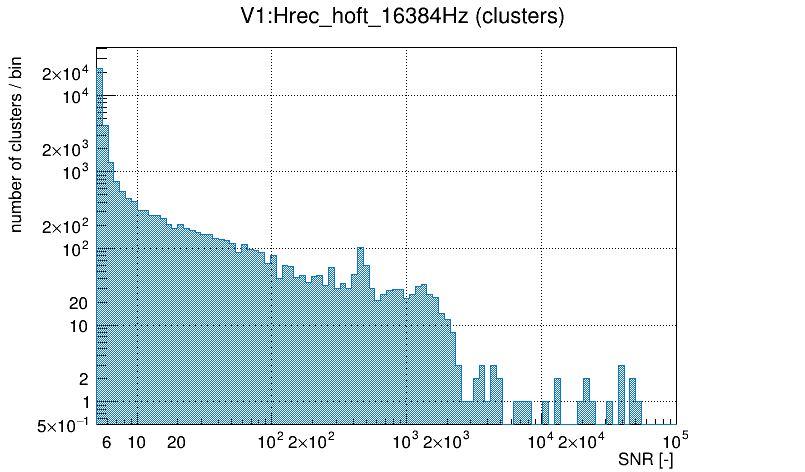

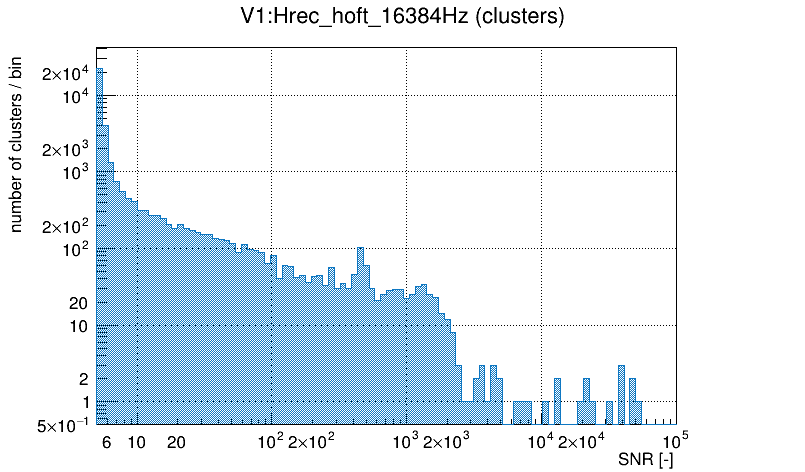

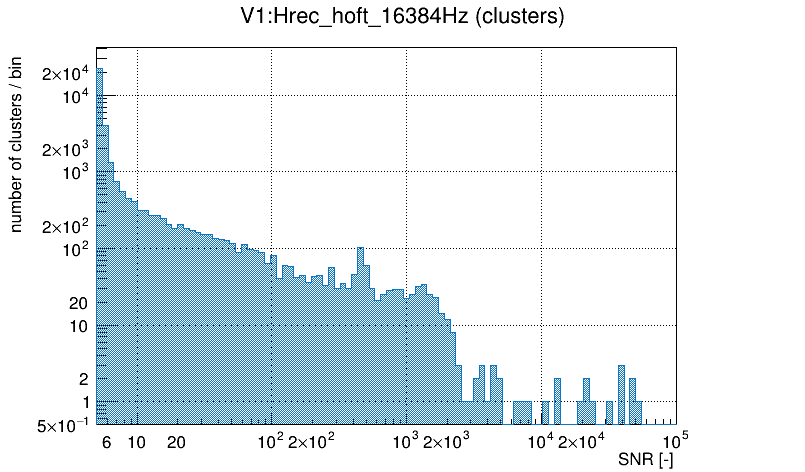

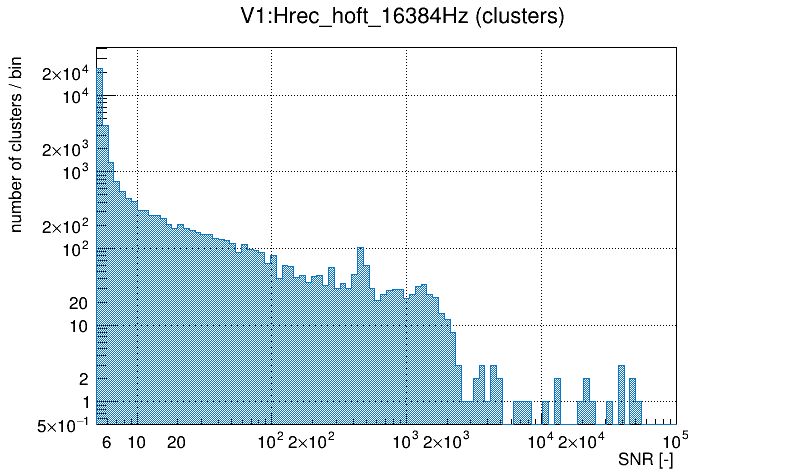

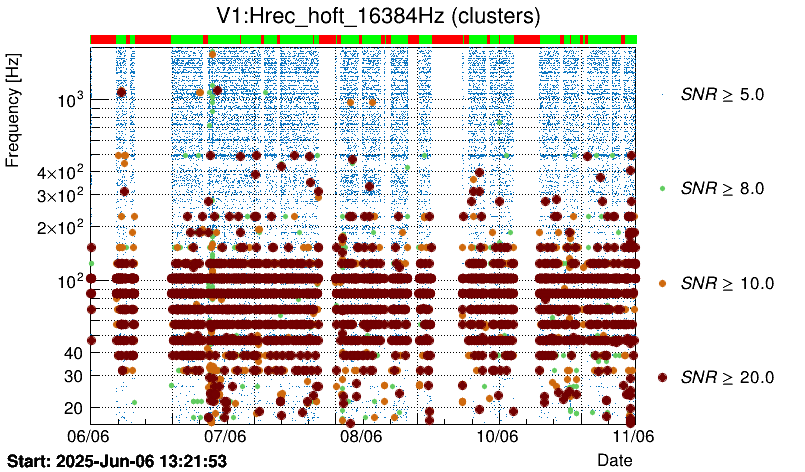

| V1:Hrec_hoft_16384Hz: 34915 clusters |

|---|

| V0 → V1:ASC_CMRF_B1_I_0, vetoed clusters: 73 (0.209 %) |

| V1 → V1:ASC_PR_DOF_TX_CORR_0, vetoed clusters: 21 (0.060 %) |

| V2 → V1:ASC_PR_TX_0, vetoed clusters: 21 (0.060 %) |

| V3 → V1:ASC_PR_TX_ERR_0, vetoed clusters: 21 (0.060 %) |

| V4 → V1:ASC_PR_TX_IN_0, vetoed clusters: 21 (0.060 %) |

| V5 → V1:ASC_PR_TX_INPUT_0, vetoed clusters: 21 (0.060 %) |

| V6 → V1:ASC_PR_TX_OUT_0, vetoed clusters: 21 (0.060 %) |

| V7 → V1:ASC_PR_TX_CORR_0, vetoed clusters: 20 (0.057 %) |

| V8 → V1:ASC_DIFFp_TX_INPUT_0, vetoed clusters: 15 (0.043 %) |