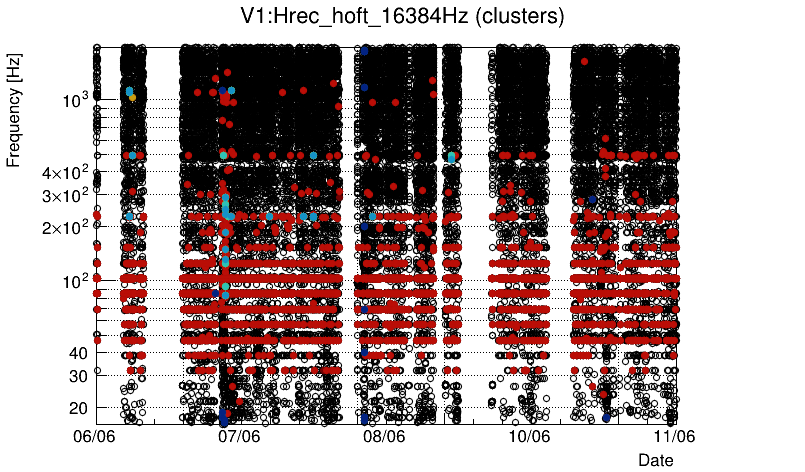

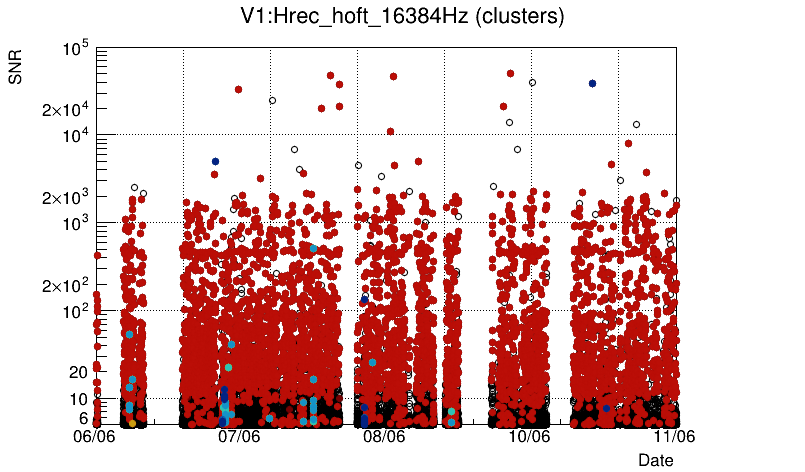

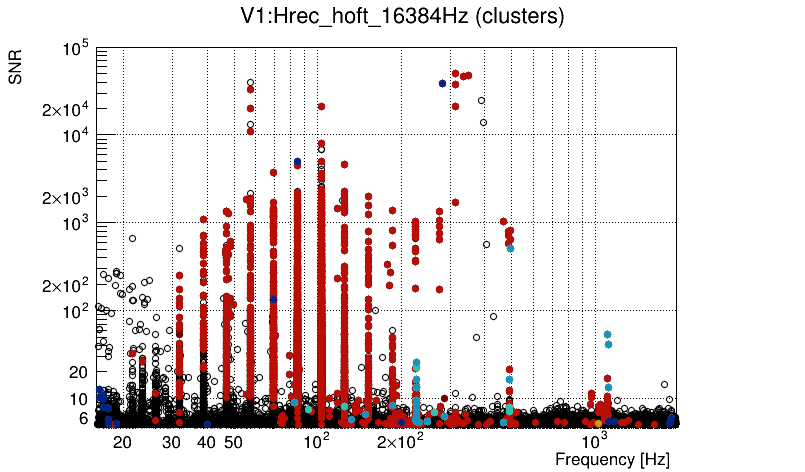

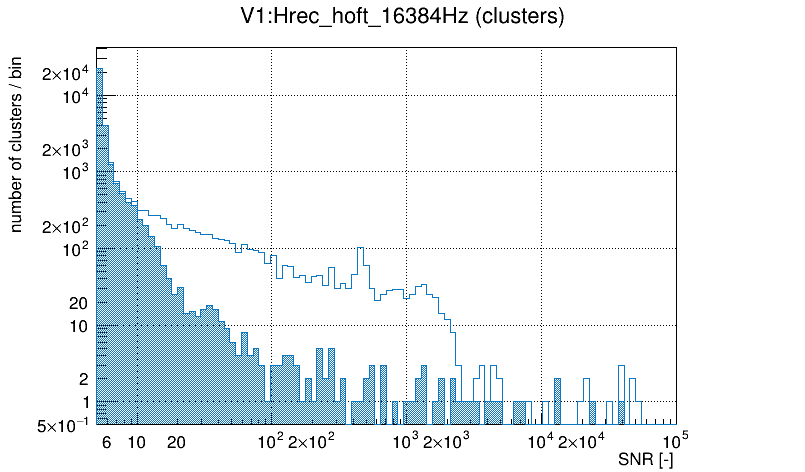

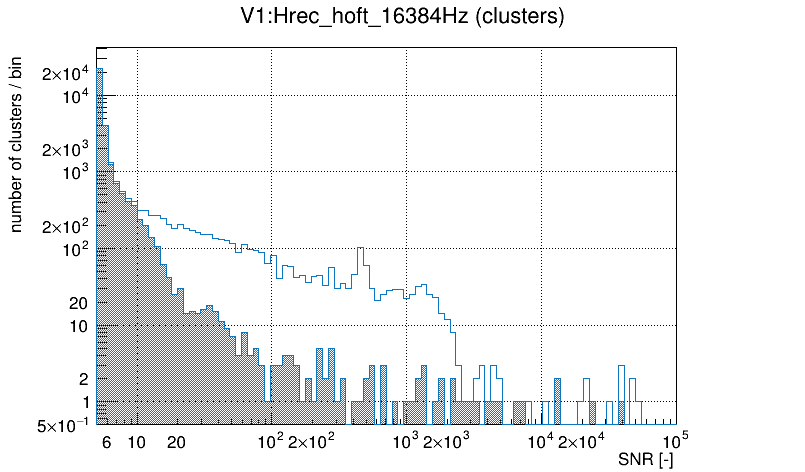

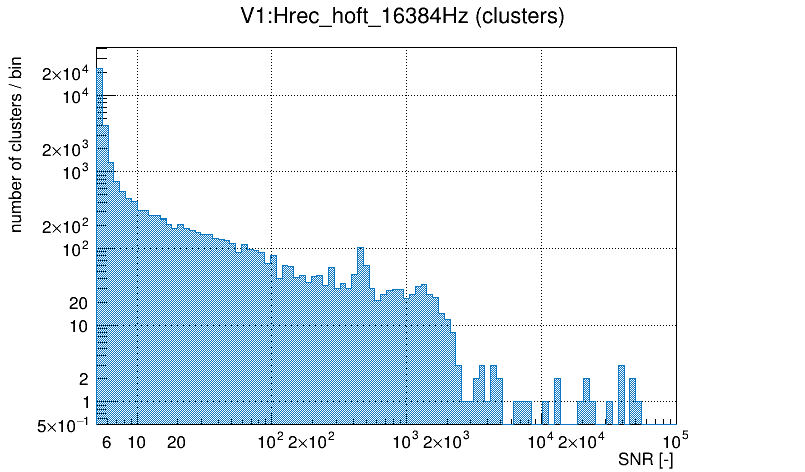

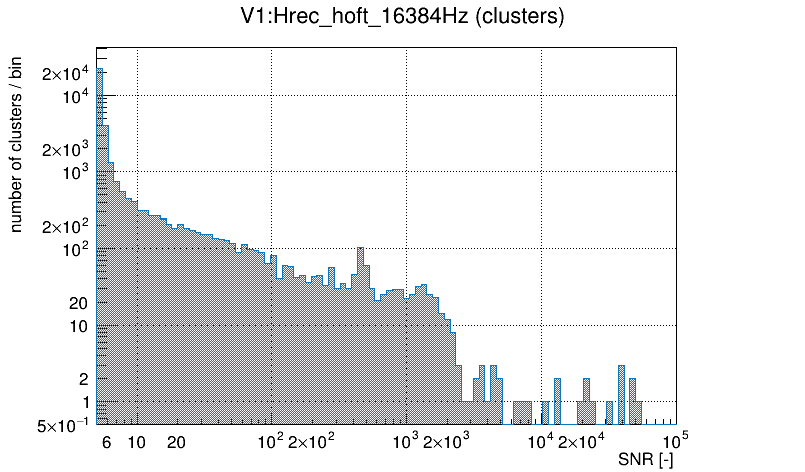

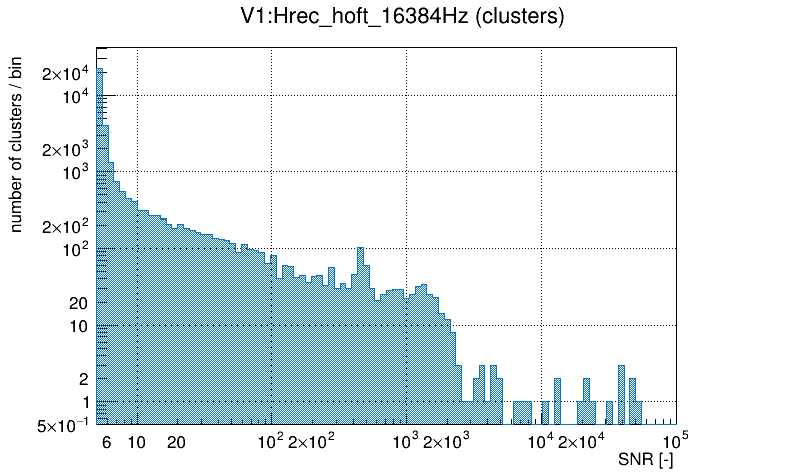

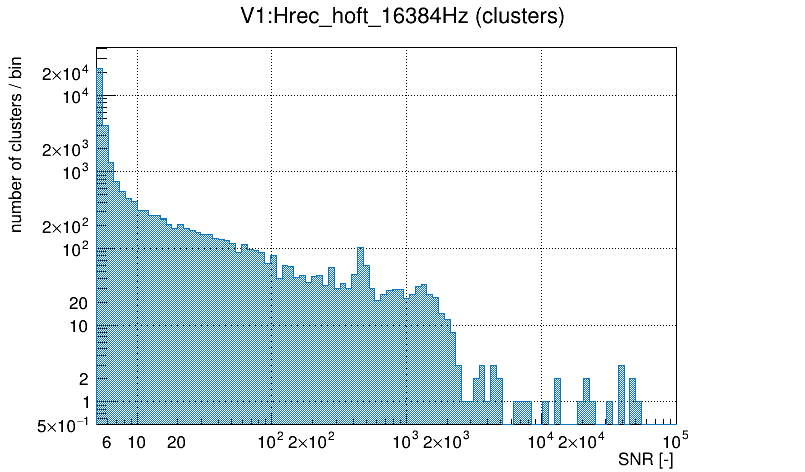

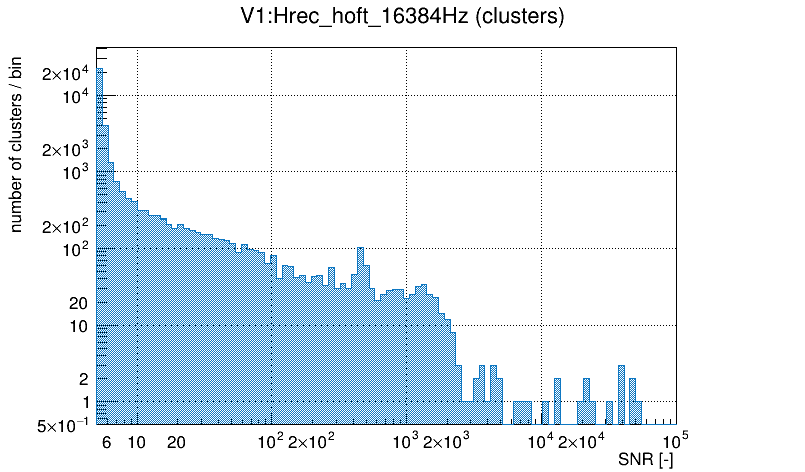

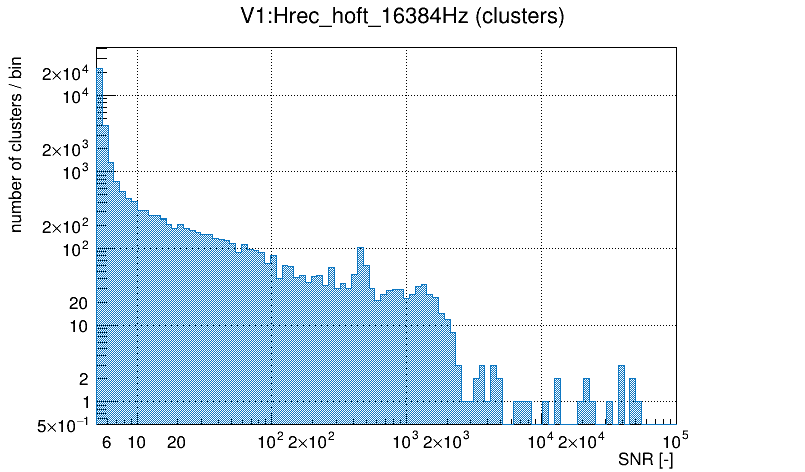

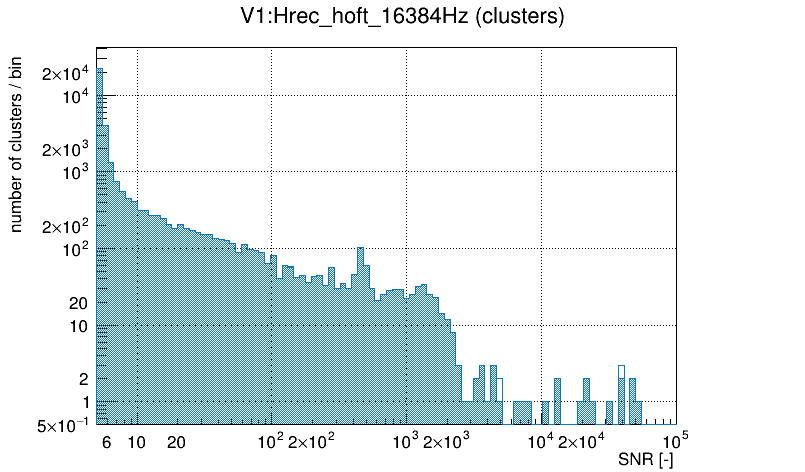

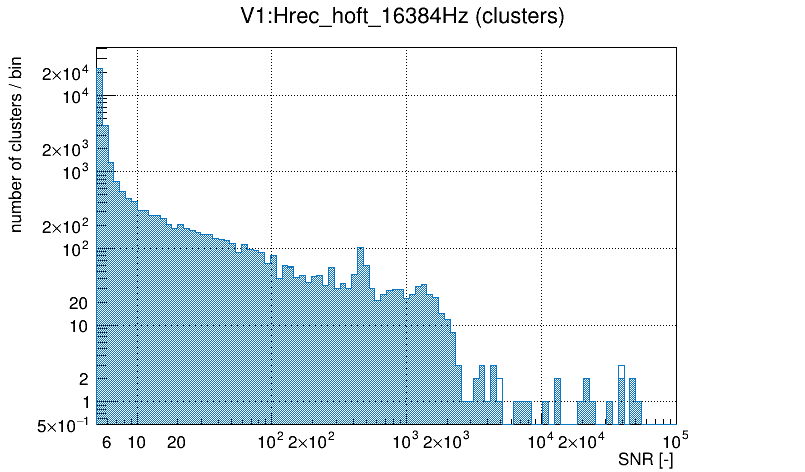

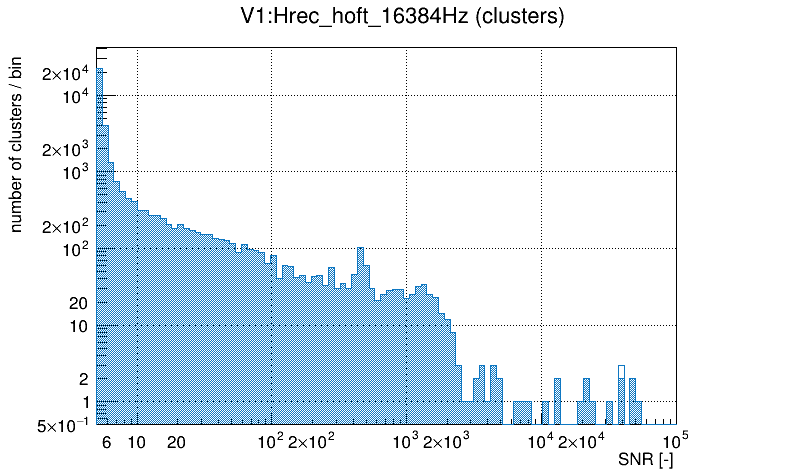

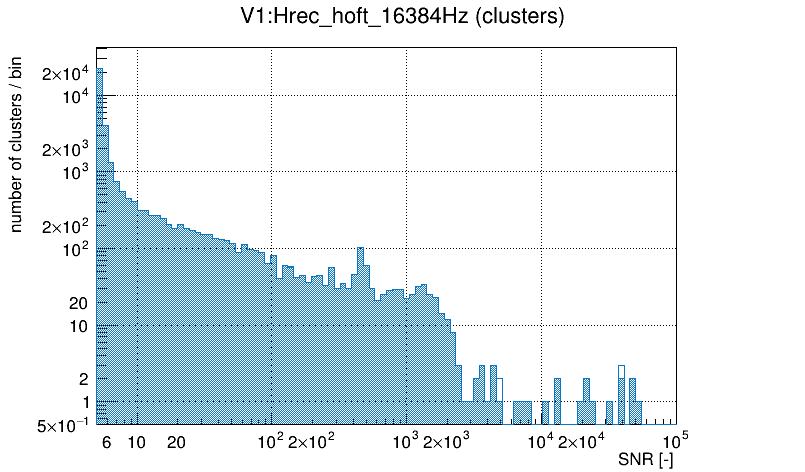

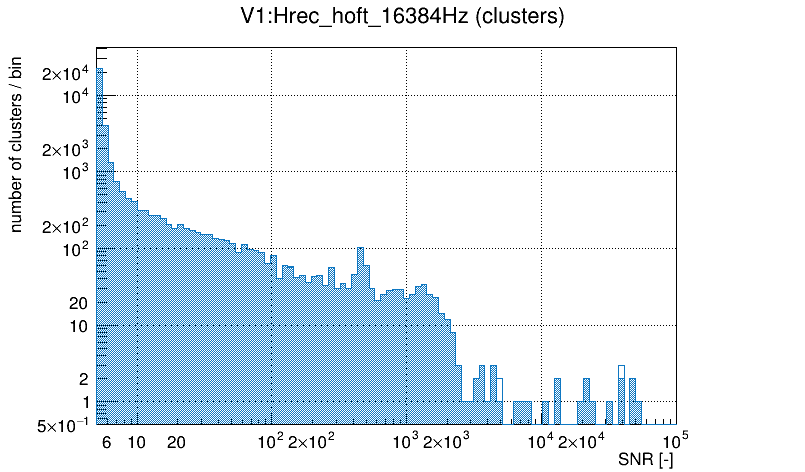

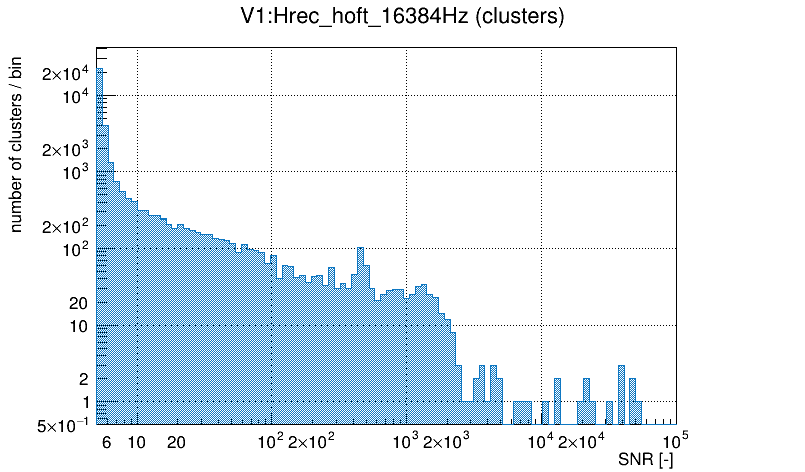

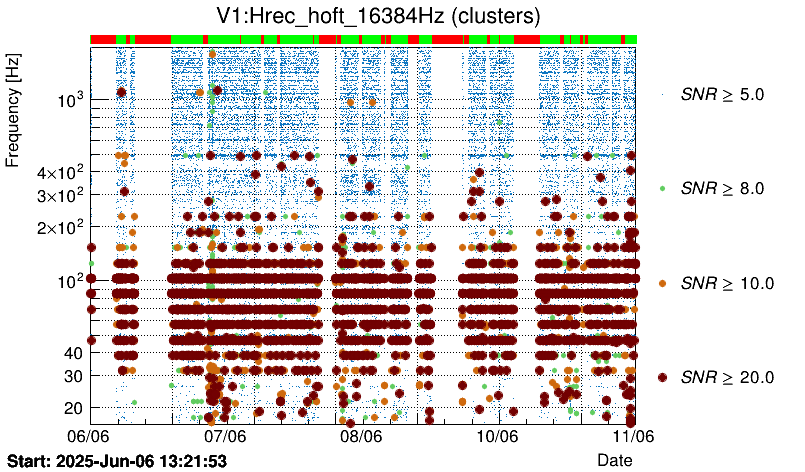

| V1:Hrec_hoft_16384Hz: 34915 clusters |

|---|

| V0 → V1:LSC_WE_CORR_0, vetoed clusters: 4492 (12.866 %) |

| V1 → V1:LSC_WI_CORR_0, vetoed clusters: 4488 (12.854 %) |

| V2 → V1:LSC_PRCL_CORR_0, vetoed clusters: 28 (0.080 %) |

| V3 → V1:LSC_PRCL_CORR_raw_0, vetoed clusters: 28 (0.080 %) |

| V4 → V1:LSC_PRCL_0, vetoed clusters: 26 (0.074 %) |

| V5 → V1:LSC_PRCL_ERR_0, vetoed clusters: 26 (0.074 %) |

| V6 → V1:LSC_PRCL_INPUT_0, vetoed clusters: 26 (0.074 %) |

| V7 → V1:LSC_PRCL_DARM_flt_0, vetoed clusters: 26 (0.074 %) |

| V8 → V1:LSC_SRCL_CORR_0, vetoed clusters: 24 (0.069 %) |

| V9 → V1:LSC_SRCL_0, vetoed clusters: 23 (0.066 %) |