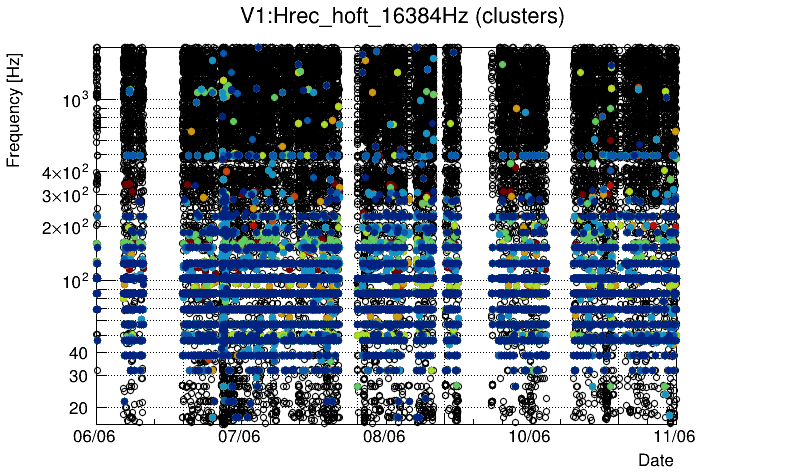

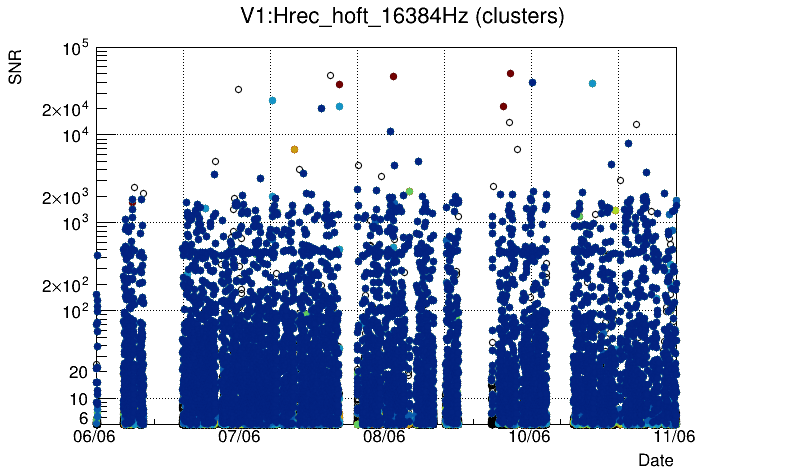

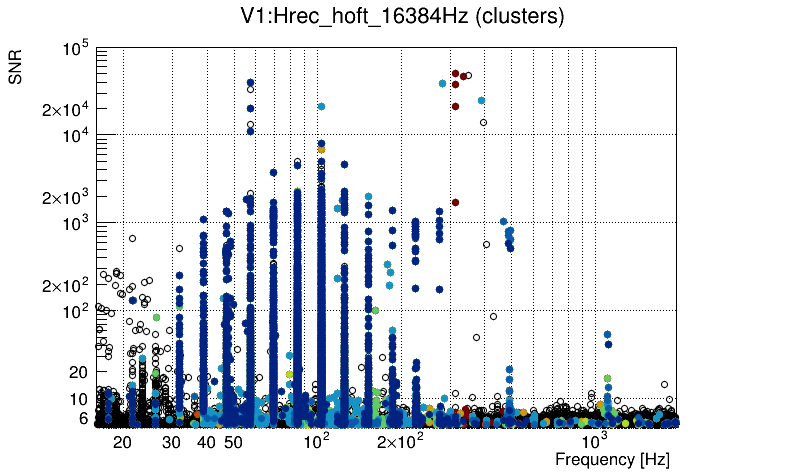

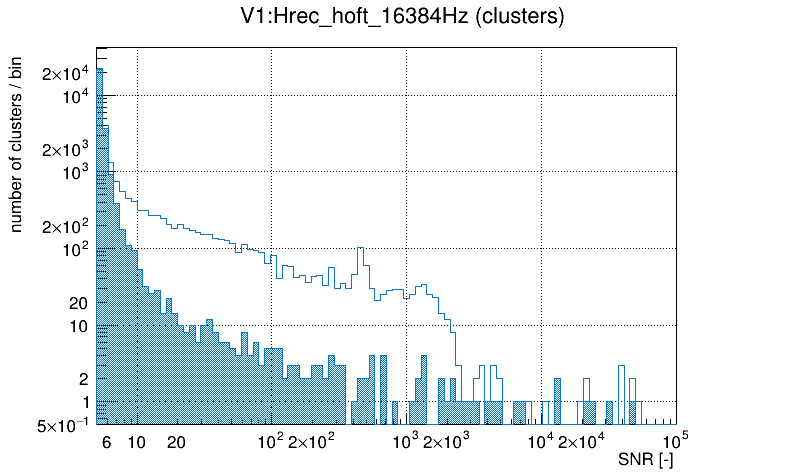

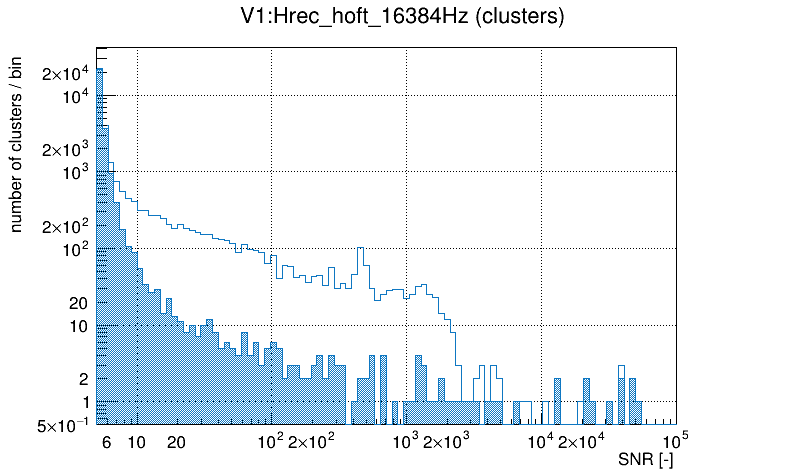

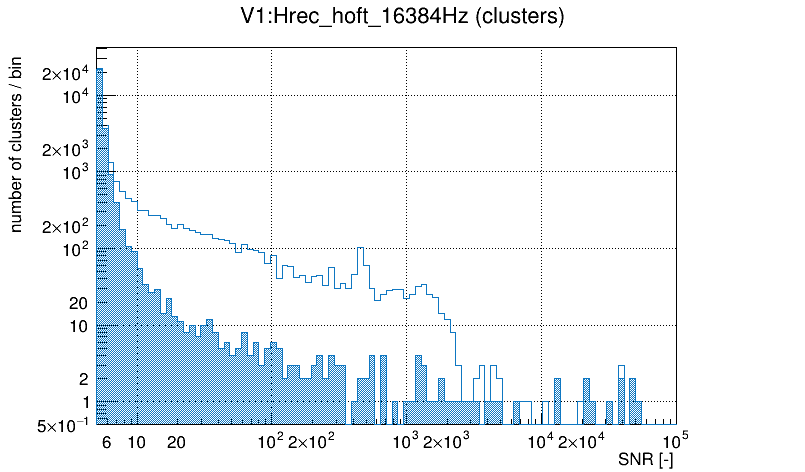

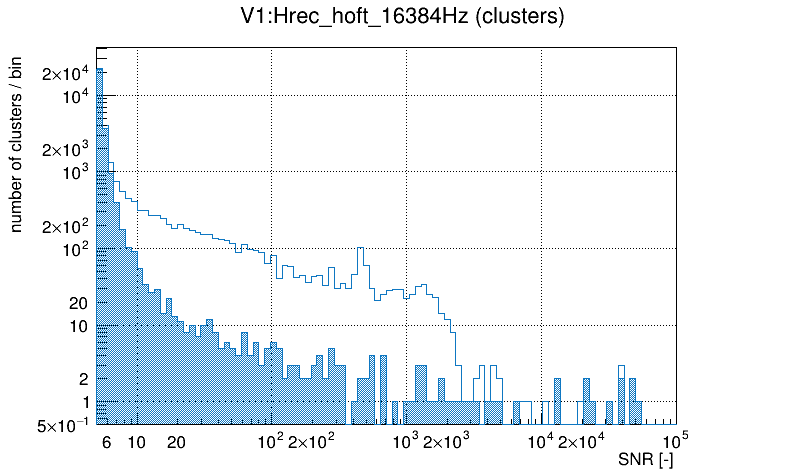

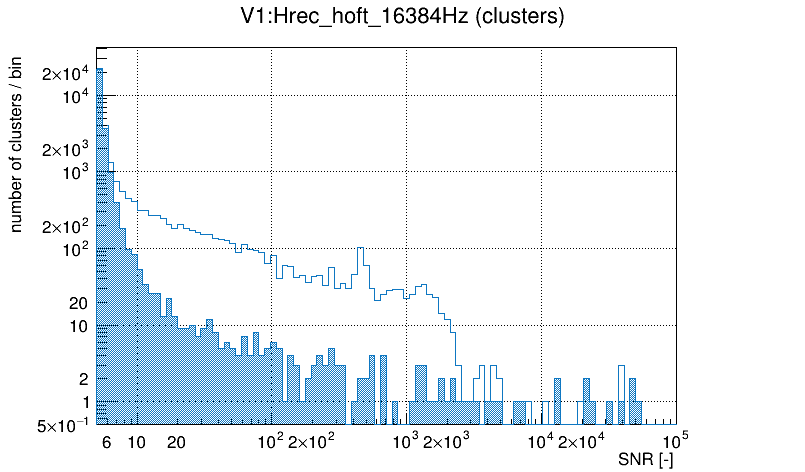

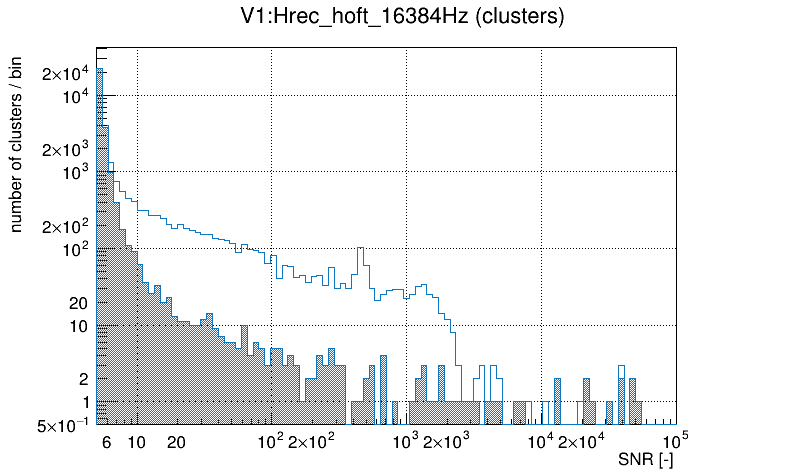

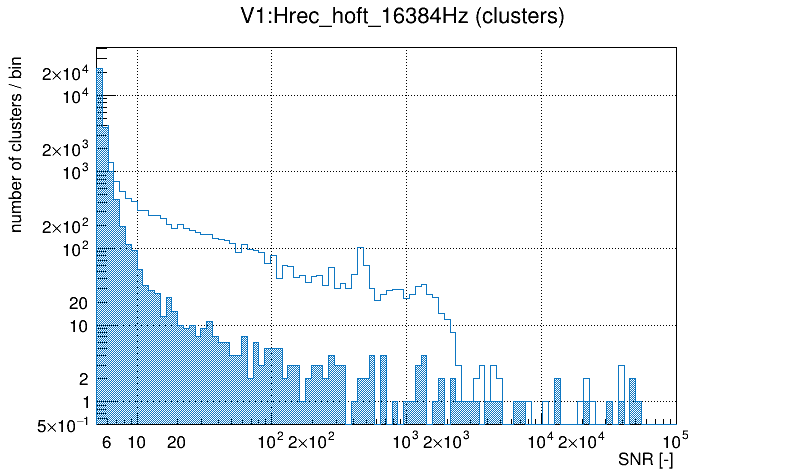

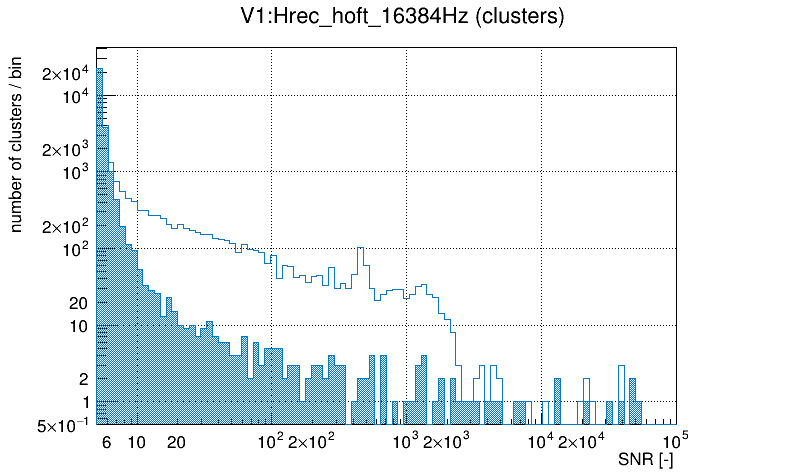

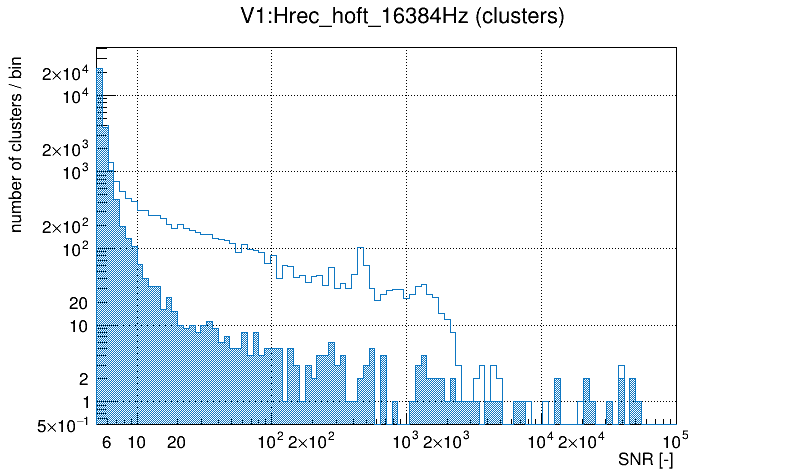

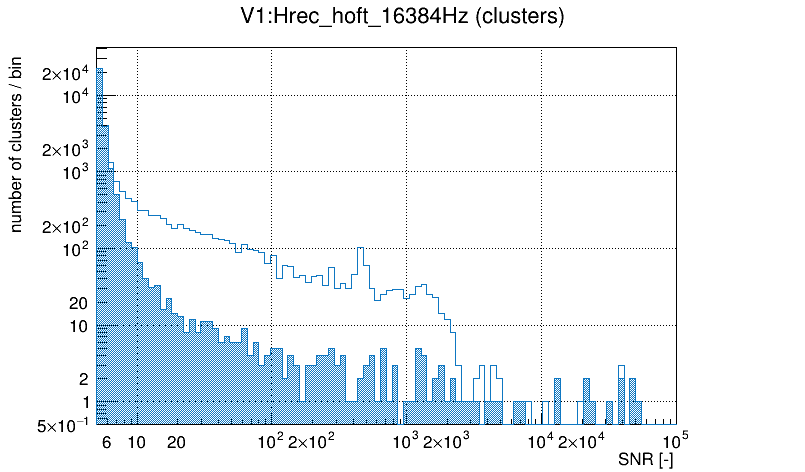

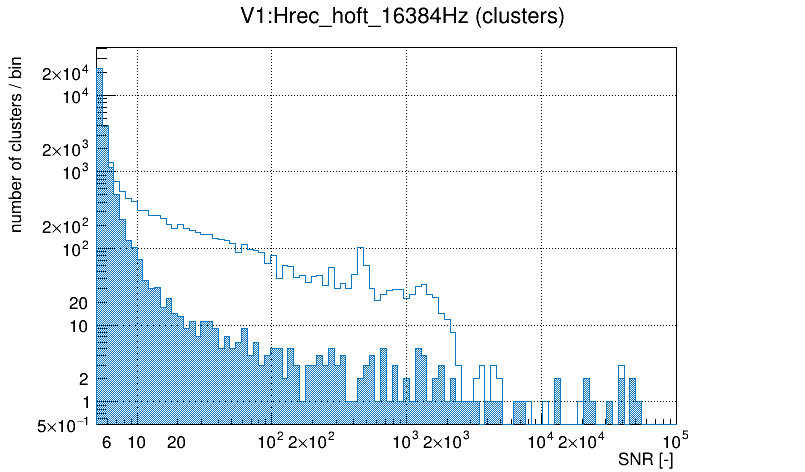

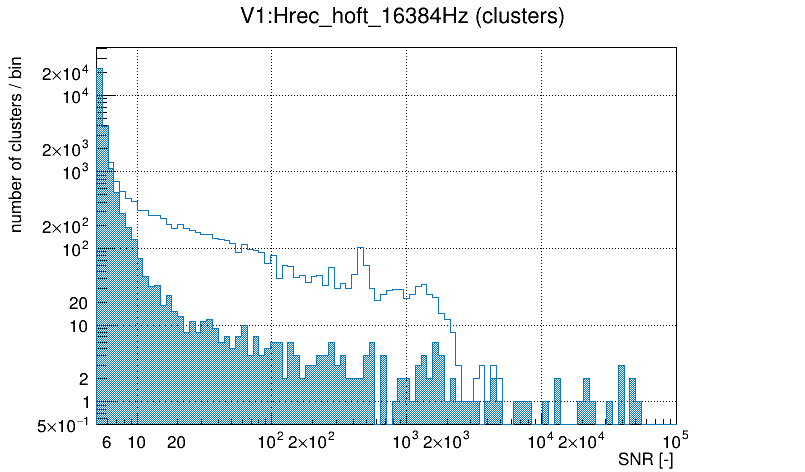

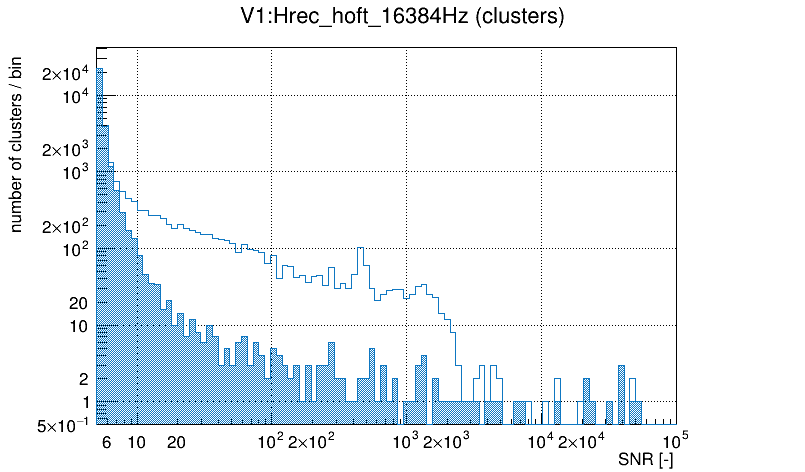

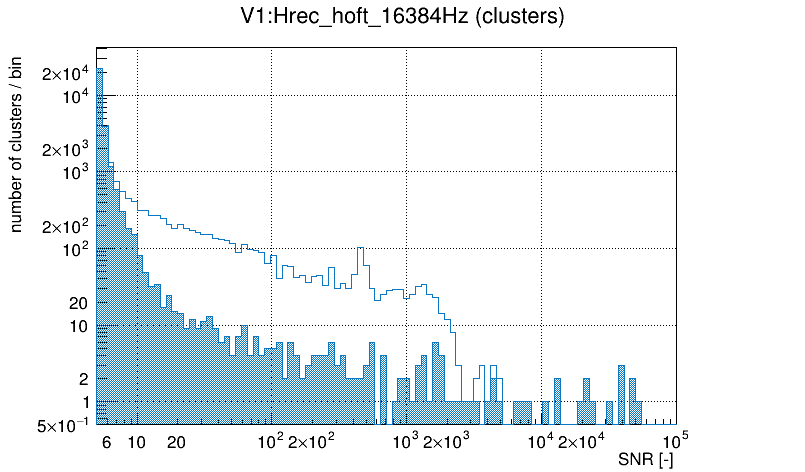

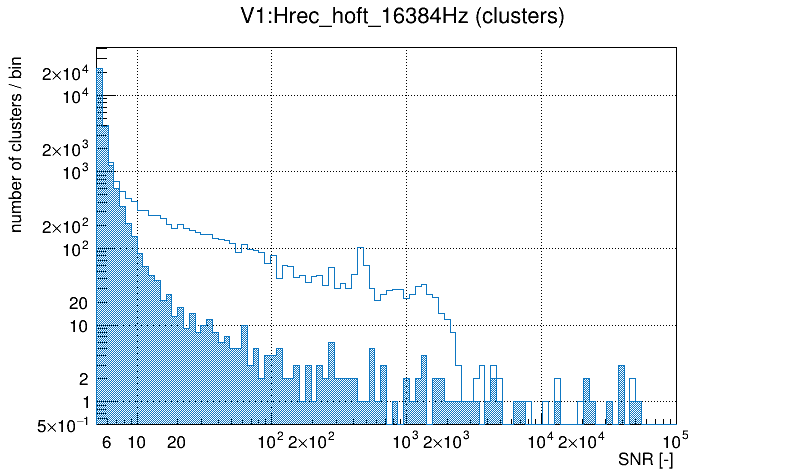

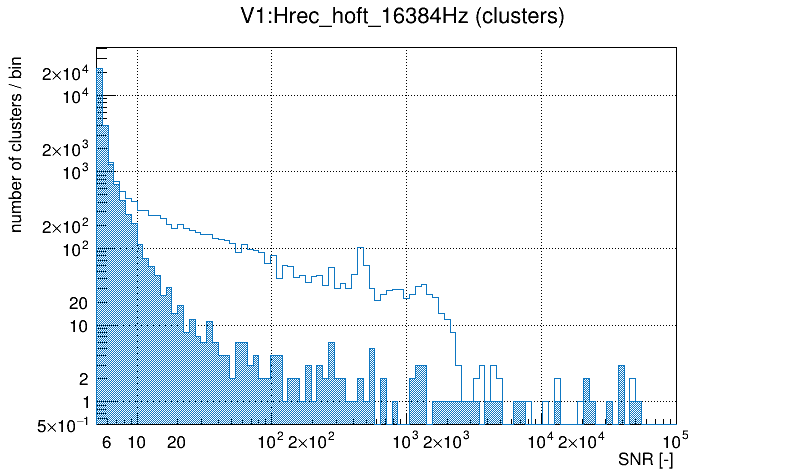

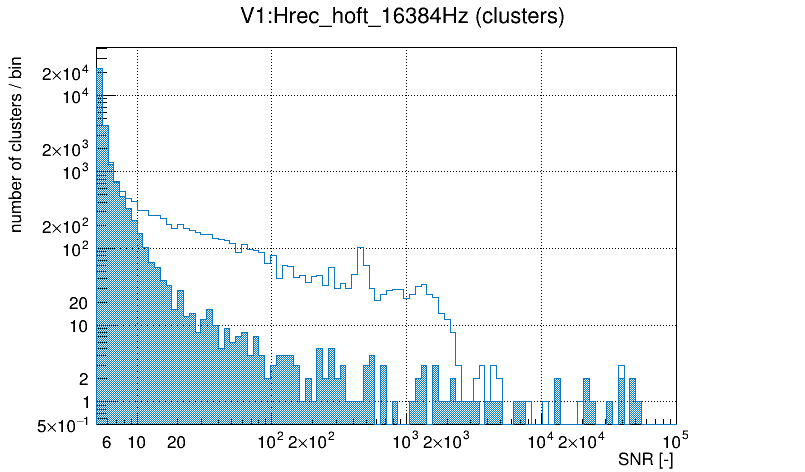

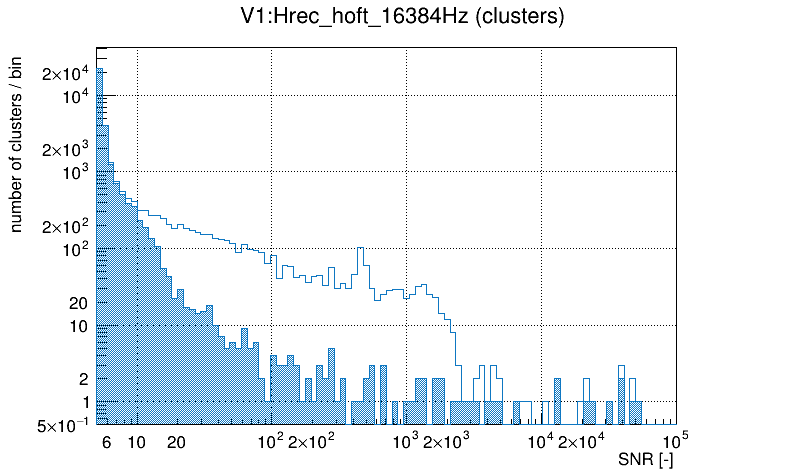

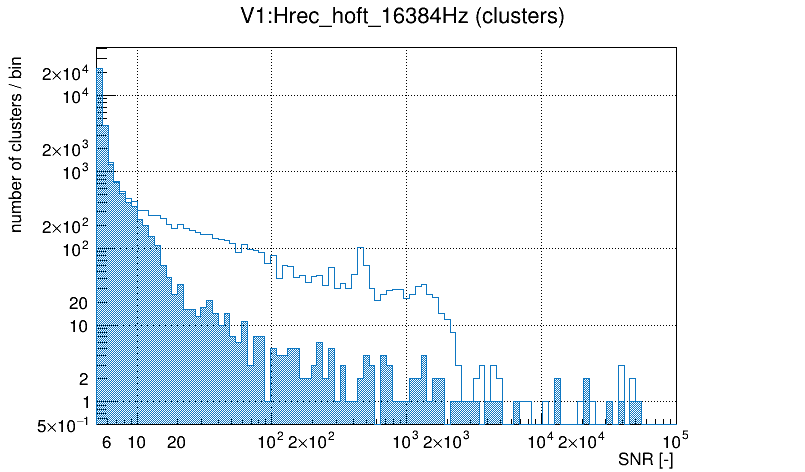

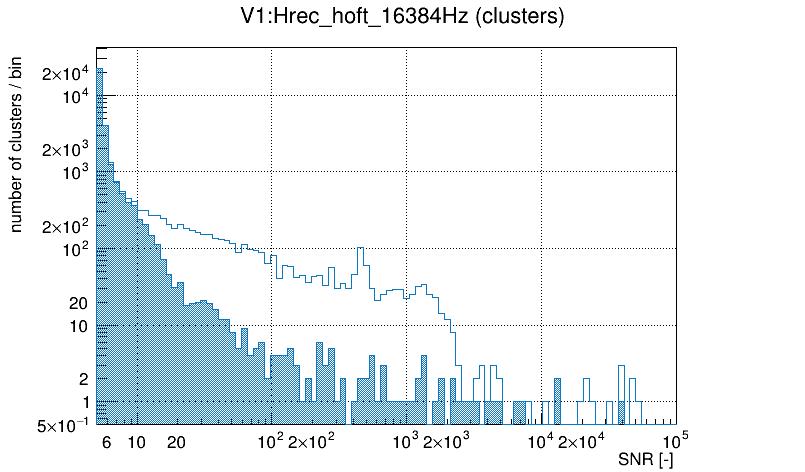

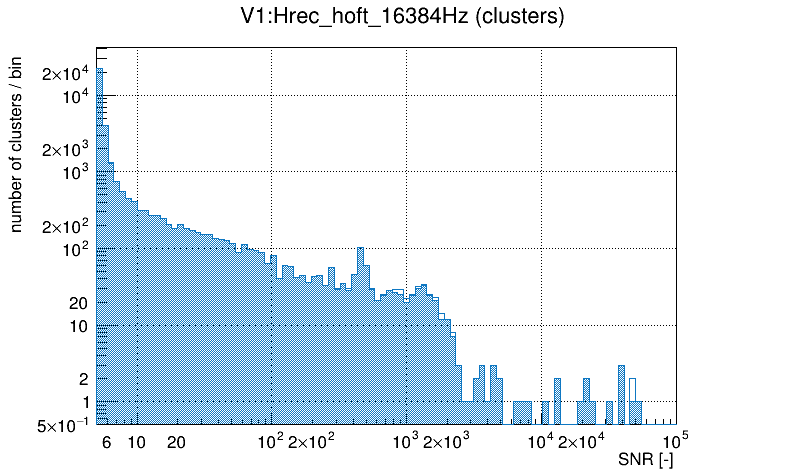

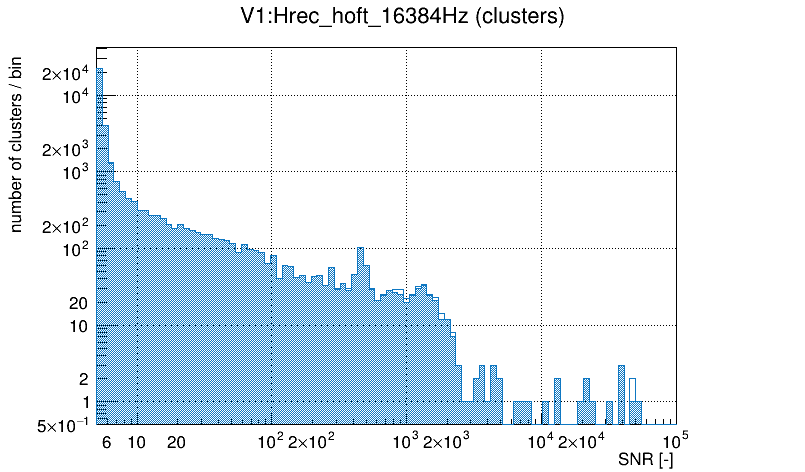

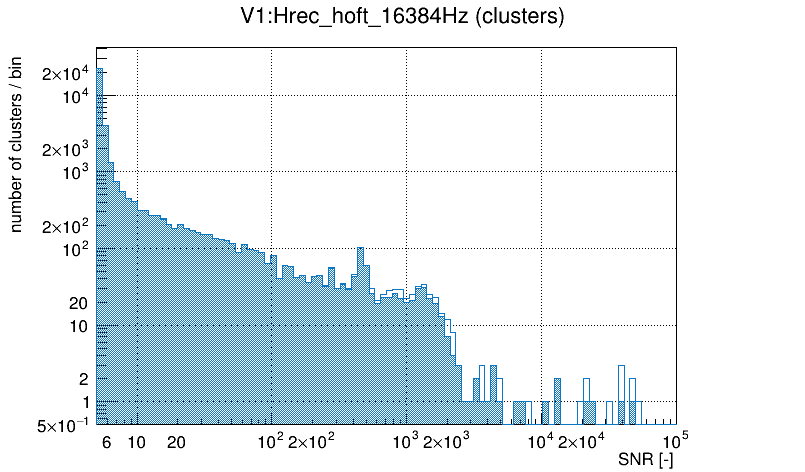

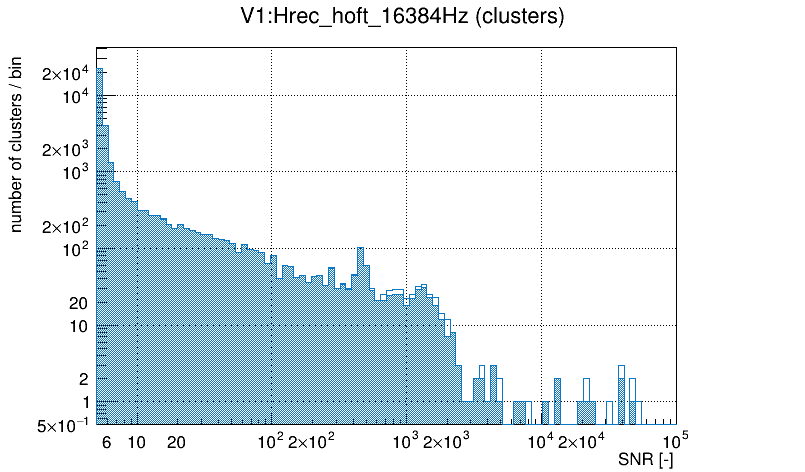

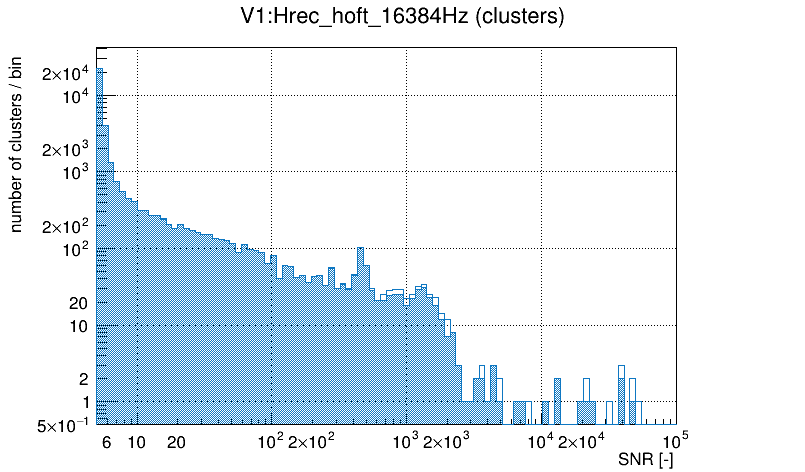

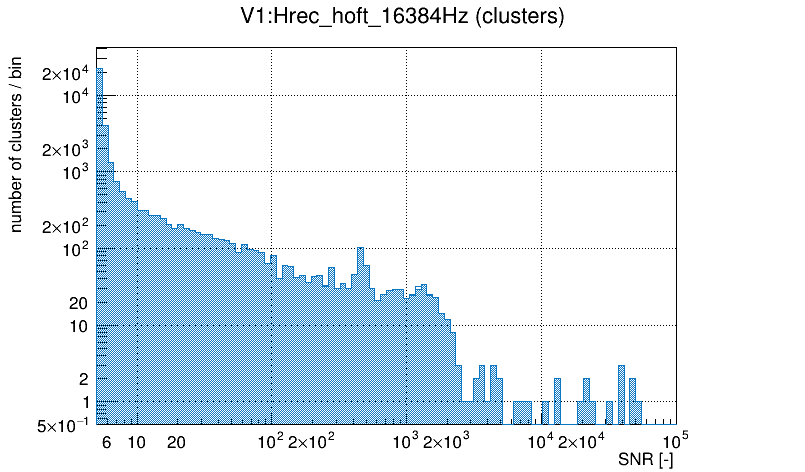

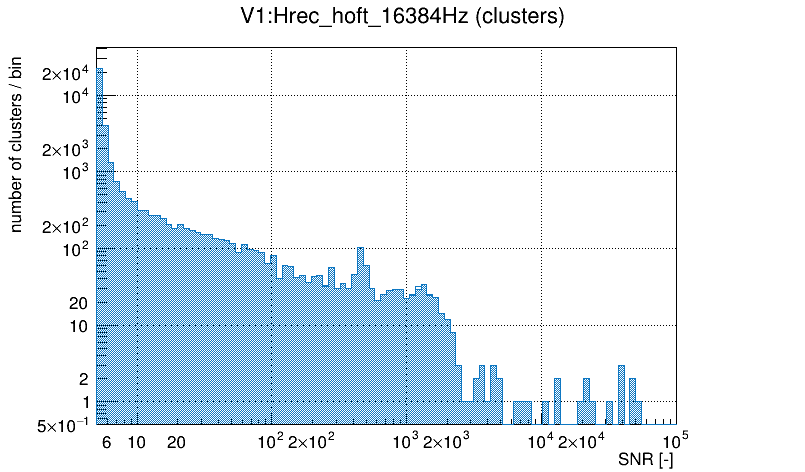

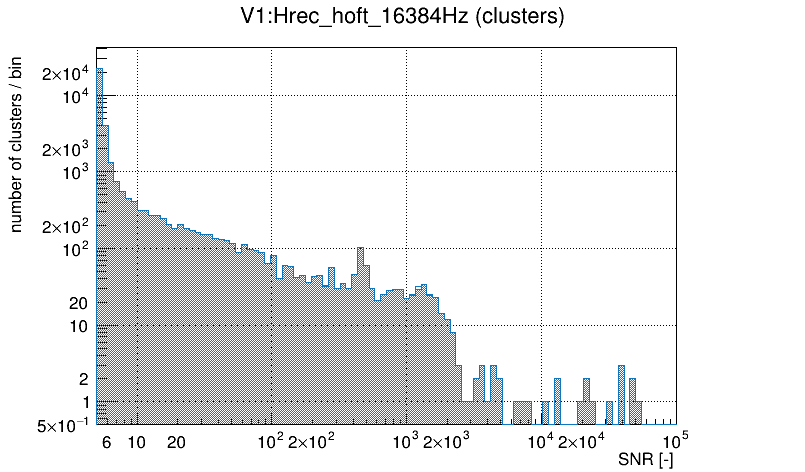

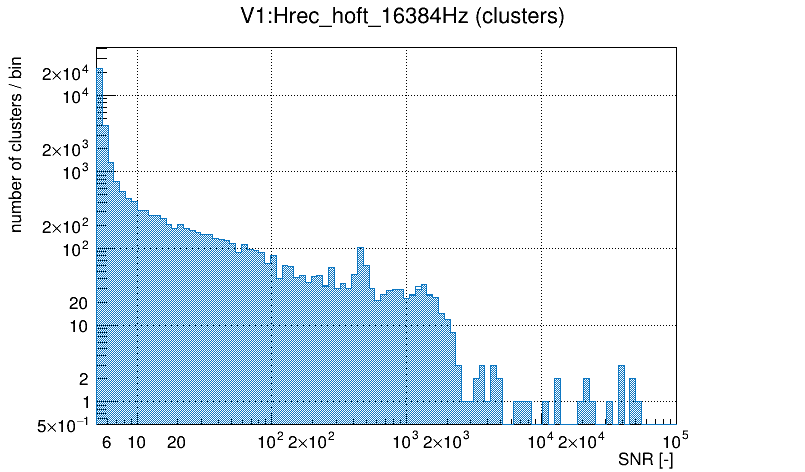

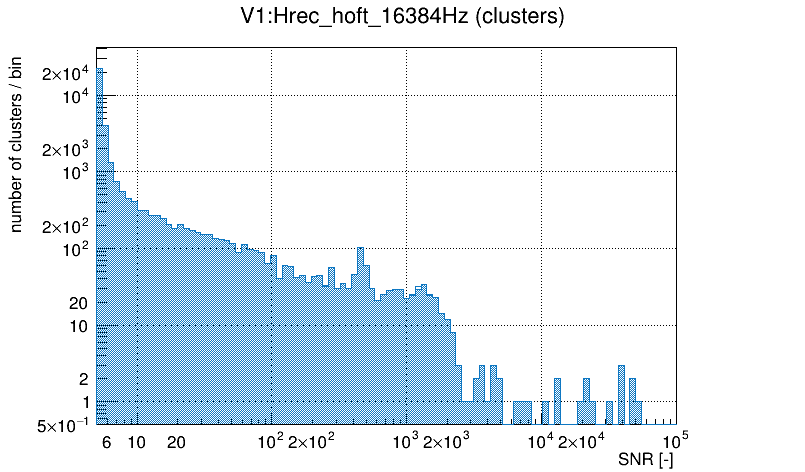

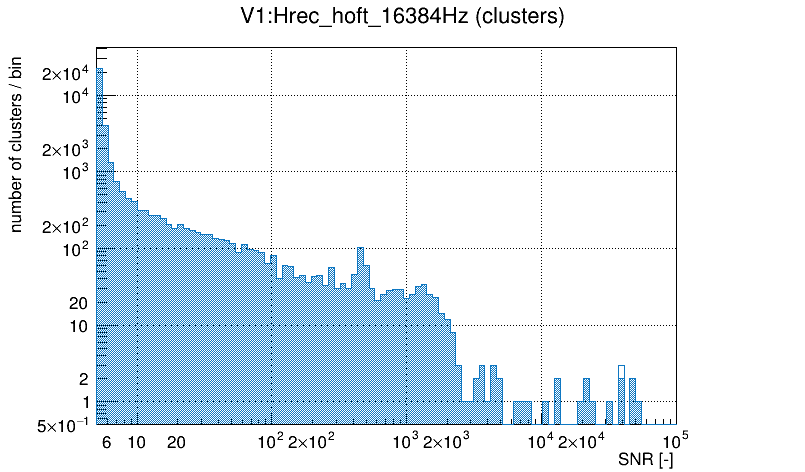

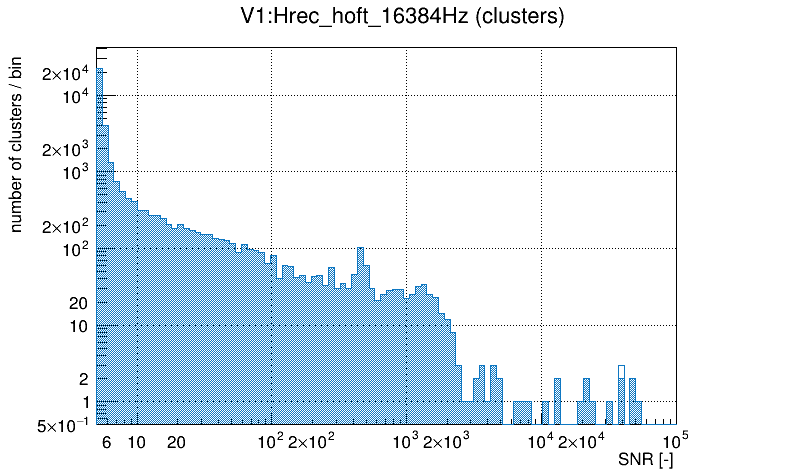

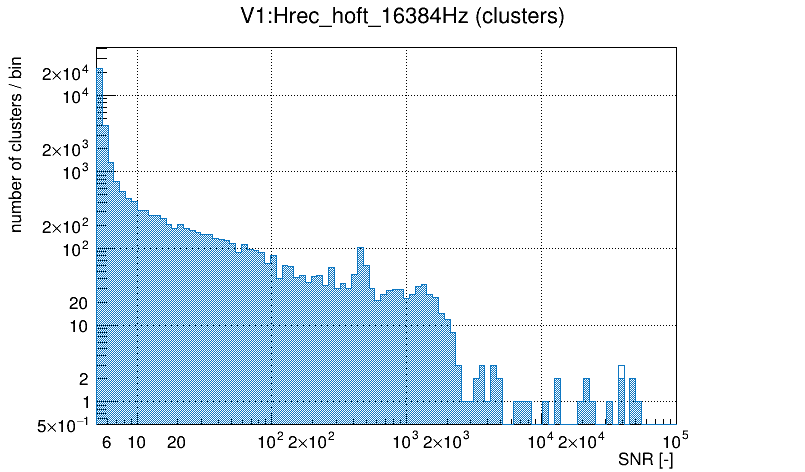

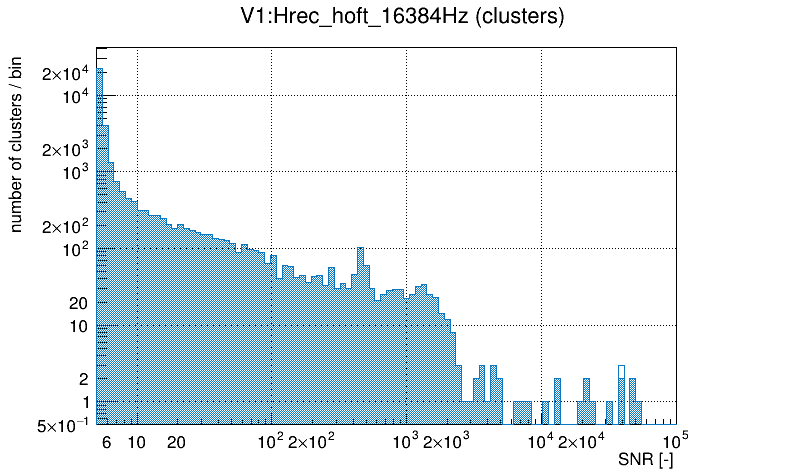

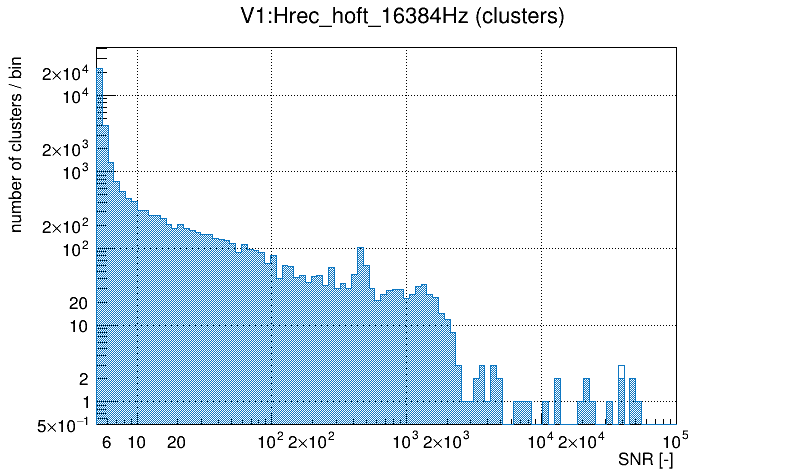

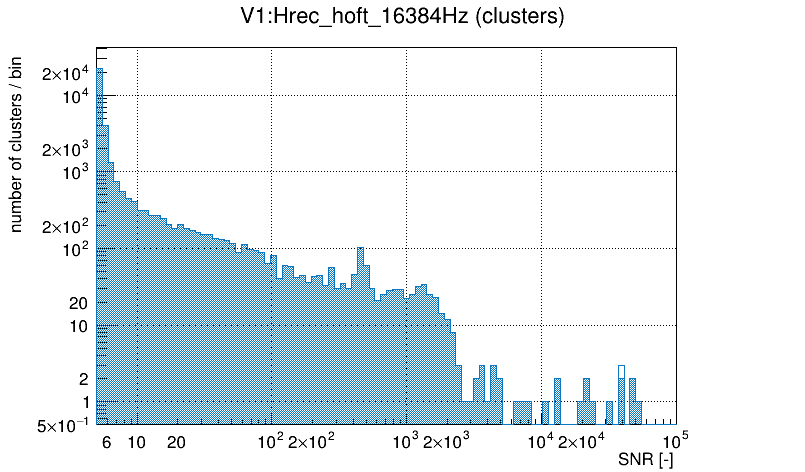

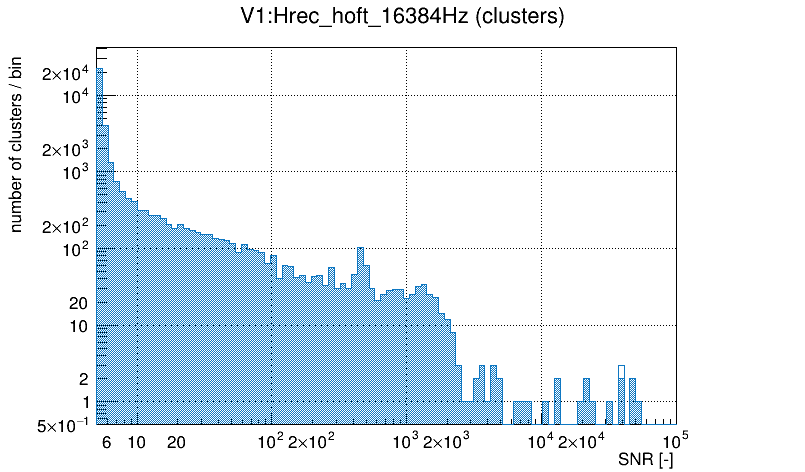

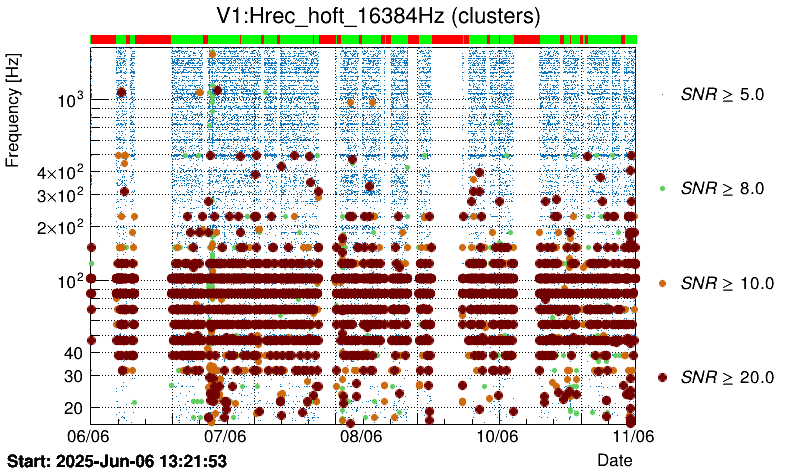

| V1:Hrec_hoft_16384Hz: 34915 clusters |

|---|

| V0 → V1:LSC_DARM_ERR_0, vetoed clusters: 7413 (21.232 %) |

| V1 → V1:LSC_B1_DC_0, vetoed clusters: 7359 (21.077 %) |

| V2 → V1:LSC_B1_DC_IN1_0, vetoed clusters: 7350 (21.051 %) |

| V3 → V1:LSC_DARM_0, vetoed clusters: 7324 (20.977 %) |

| V4 → V1:LSC_DARM_INPUT_0, vetoed clusters: 7269 (20.819 %) |

| V5 → V1:LSC_DARM_CORR_raw_0, vetoed clusters: 7071 (20.252 %) |

| V6 → V1:LSC_B1_DC_IN2_0, vetoed clusters: 7015 (20.092 %) |

| V7 → V1:LSC_B1_DC_INPUT_0, vetoed clusters: 7015 (20.092 %) |

| V8 → V1:LSC_DCP_DARM_CORR_FLT_LF_0, vetoed clusters: 6683 (19.141 %) |

| V9 → V1:LSC_DCP_DARM_ERR_FLT_HF_0, vetoed clusters: 6442 (18.451 %) |