upv ./segments.txt ./parameters.txt

| UPV version: | 3.2.0: documentation gitlab repository |

| UPV run by: | unknown |

| UPV processing time: | 0 h, 32 min, 57 s |

| Processing Date: | Thu Feb 13 10:21:58 2025 (UTC) |

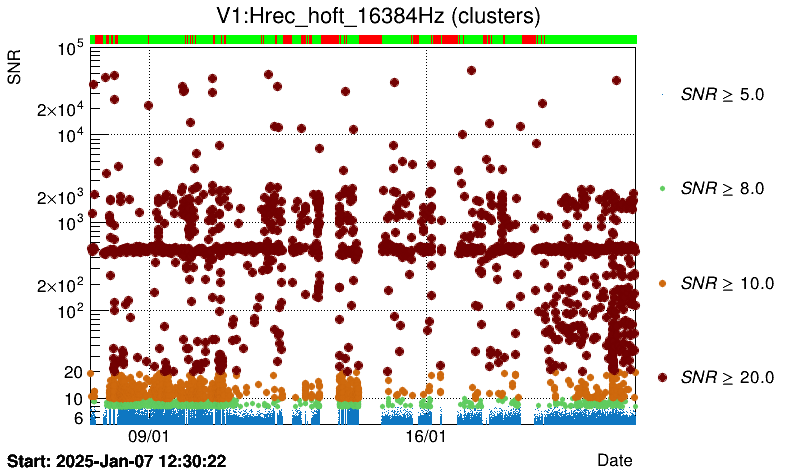

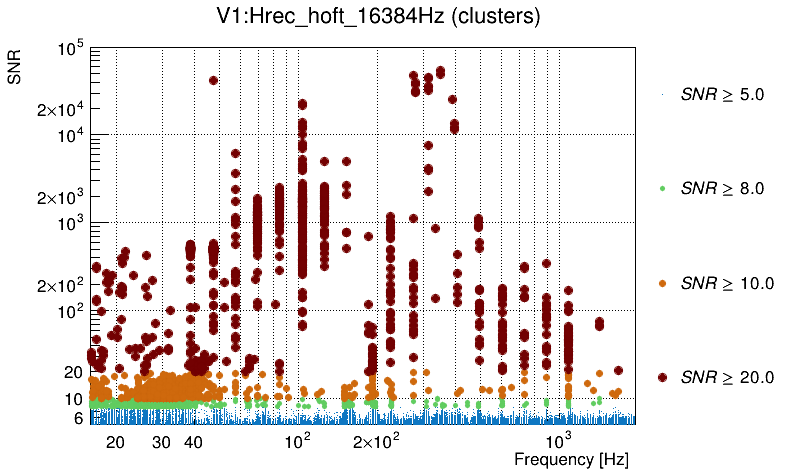

| Requested start: | 1420288240 → Tue Jan 7 12:30:22 2025 (UTC) |

| Requested stop: | 1421478029 → Tue Jan 21 07:00:11 2025 (UTC) |

| Requested livetime: | 825629 sec → 9.556 days |

| Requested segments: | upv.insegments.txt |

| Summary text file: | upv.summary.txt |

| Number of source channels: | 100 (out of 100) |

| Configuration: | upv.parameters.txt |

| Target SNR selection: | SNR > 7.000 |

| Target frequency selection: | 16.000 Hz < f < 1956.764 Hz |

| Coincidence time window: | δt = 1.000 s |

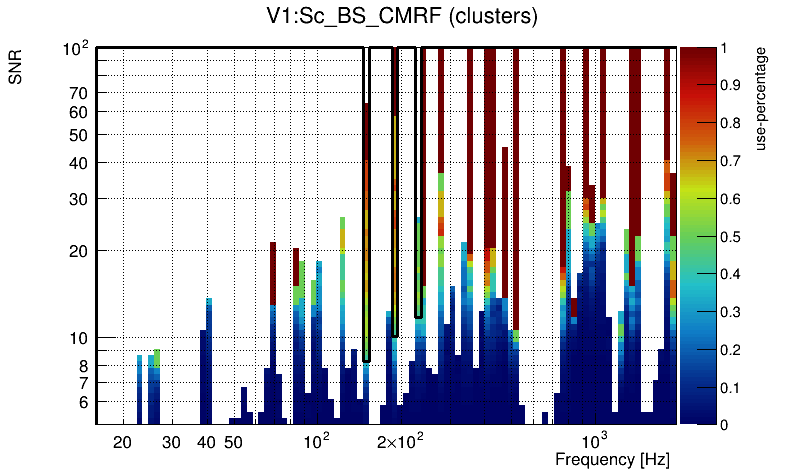

| Veto definition: | use-percentage > 0.400 (per frequency bin) |

| number of used source clusters > 10 (per frequency bin) |

|

|

|

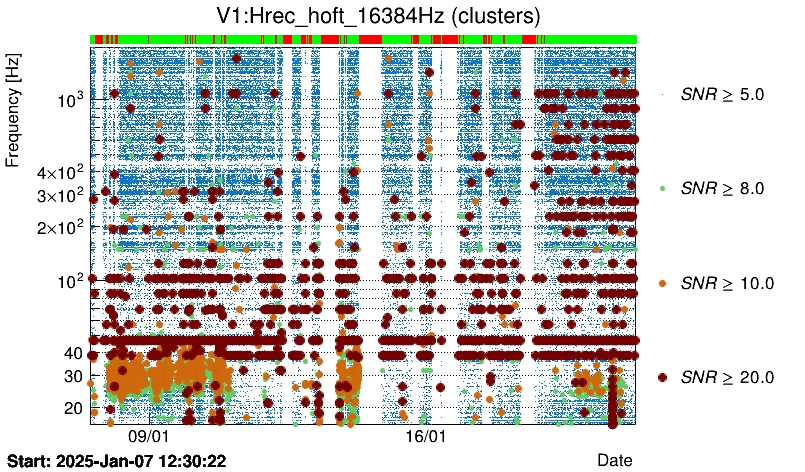

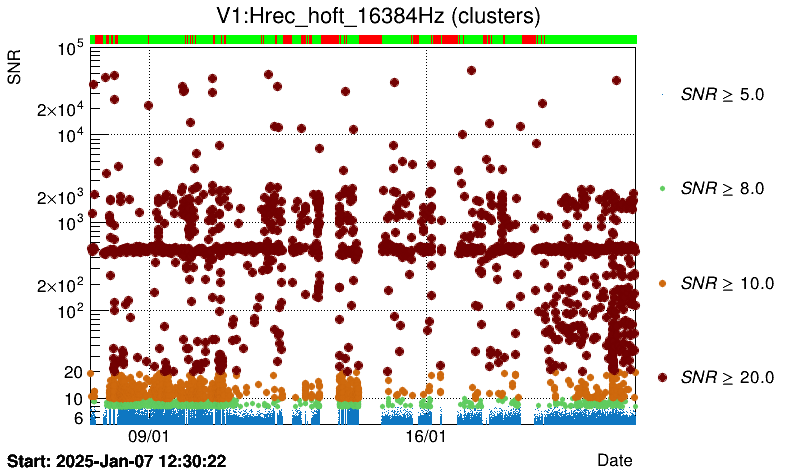

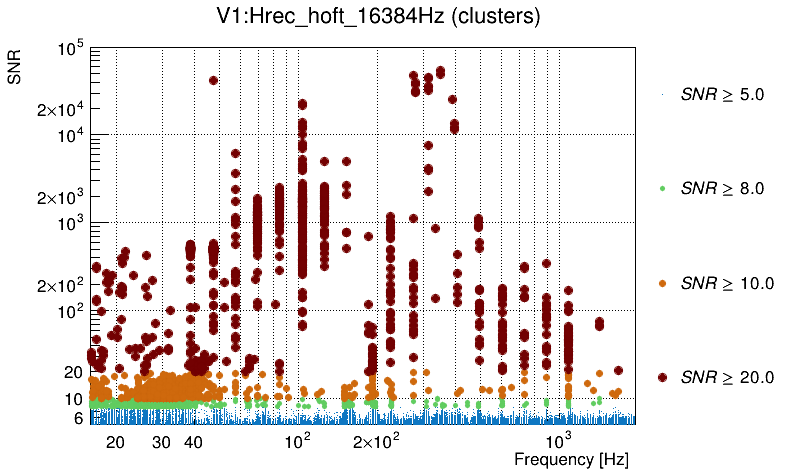

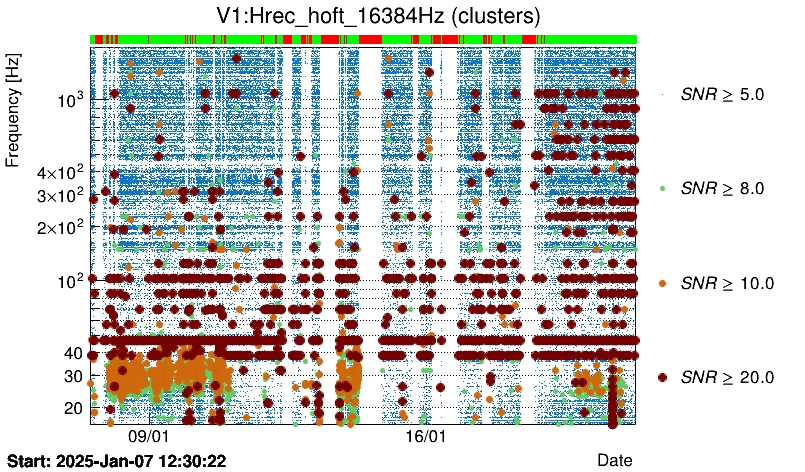

Note: these plots includes the triggers used in the VetoPerf report: the selection can be different from the one used for UPV.

The veto performance has been measured. See the VetoPerf report.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Florent Robinet, florent.robinet@ijclab.in2p3.fr |