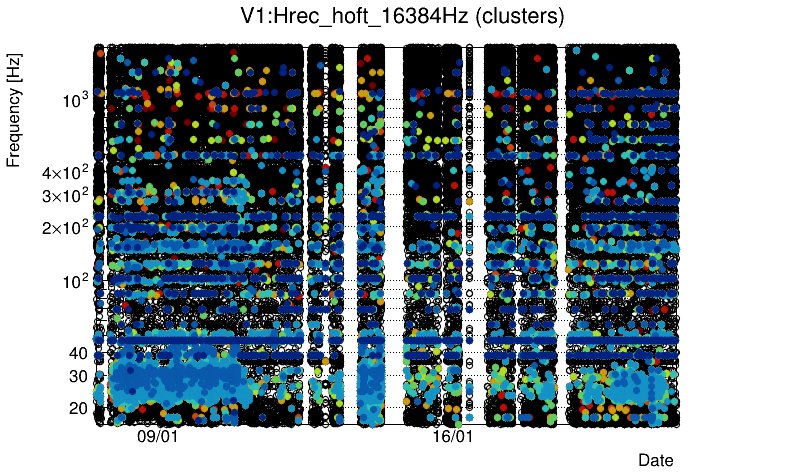

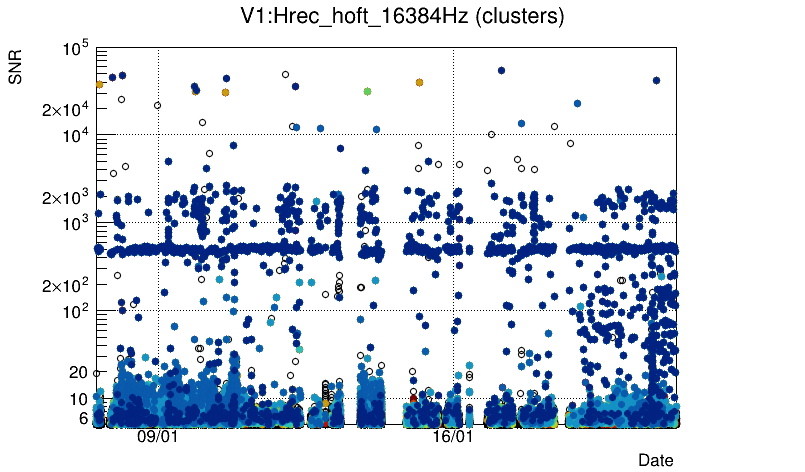

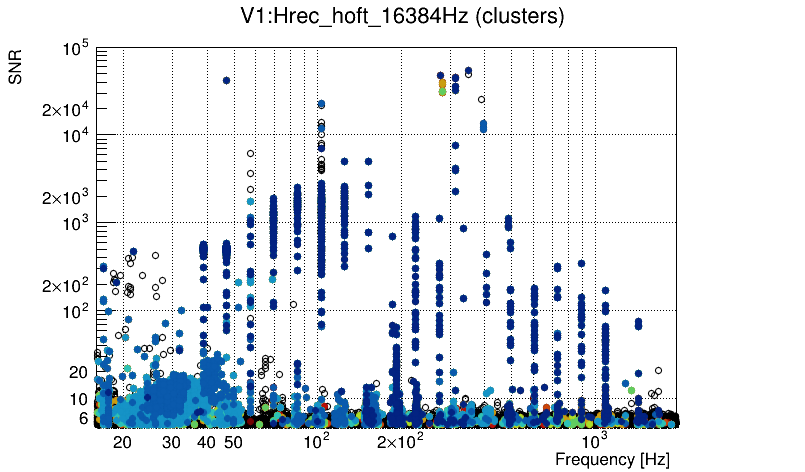

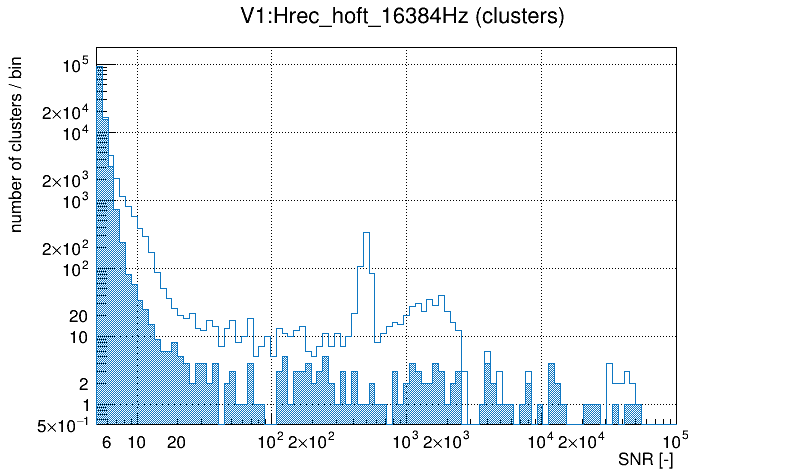

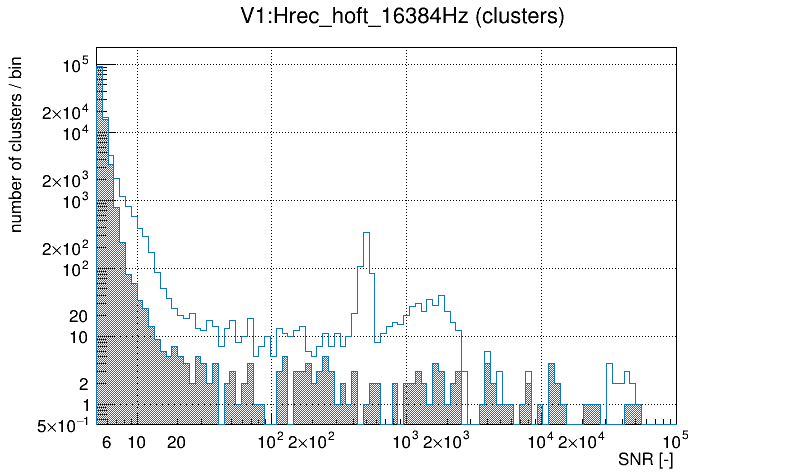

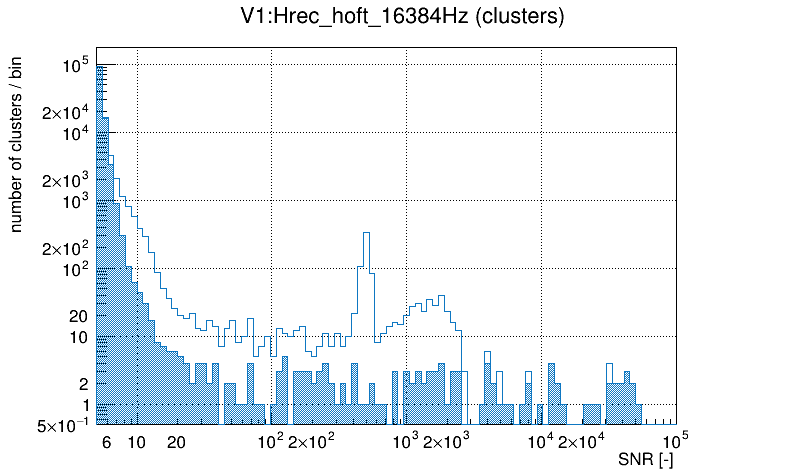

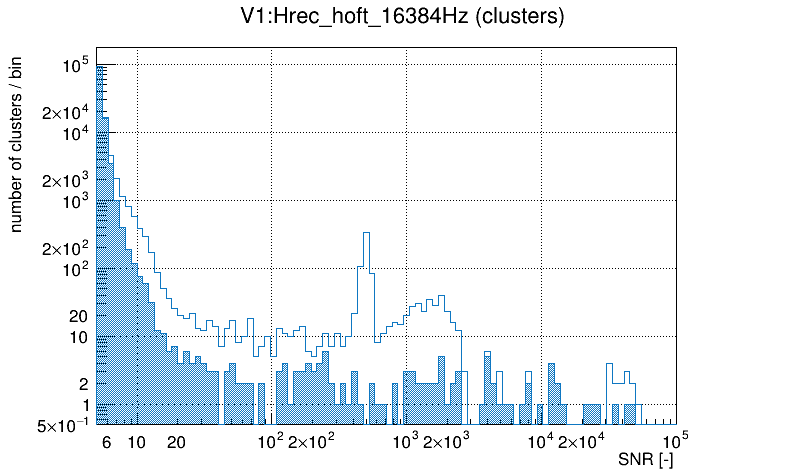

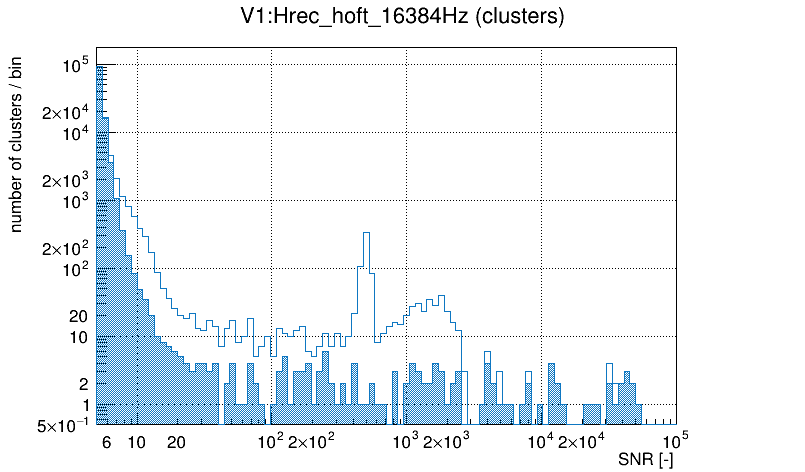

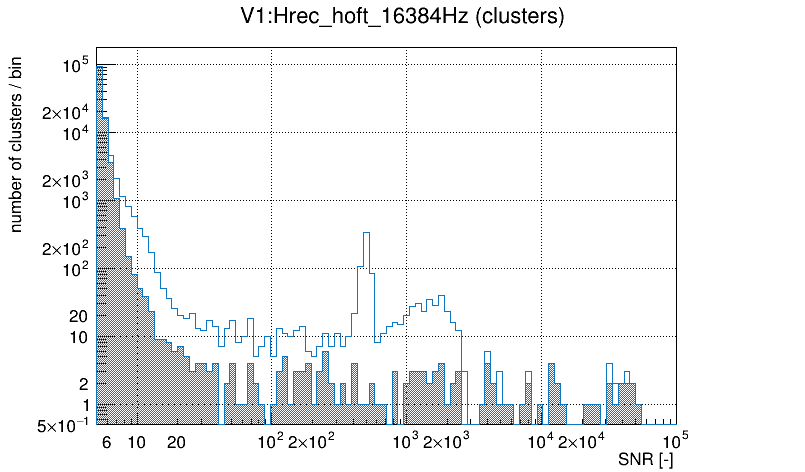

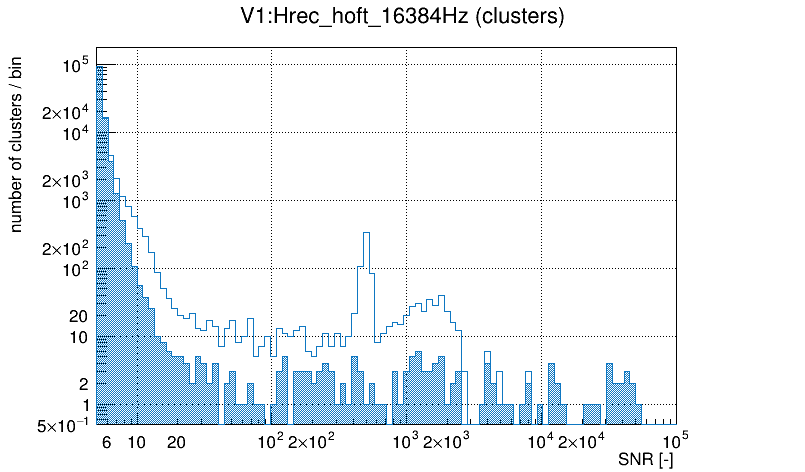

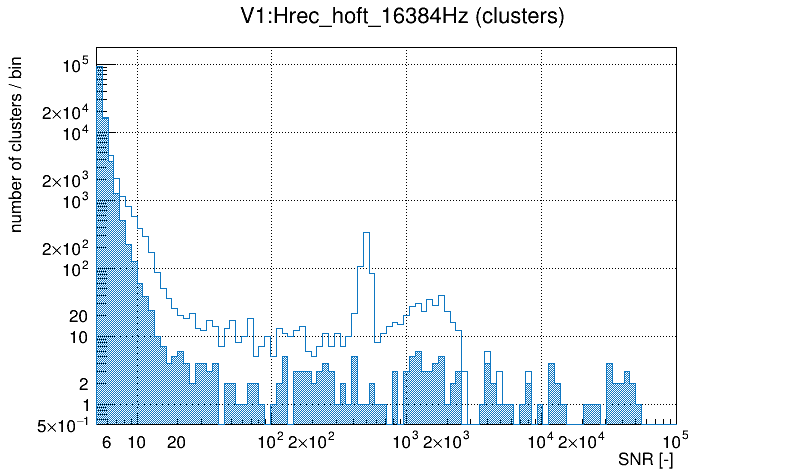

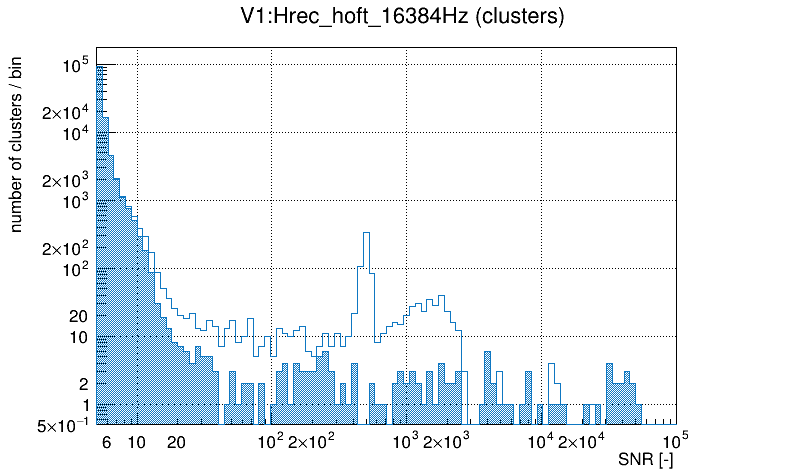

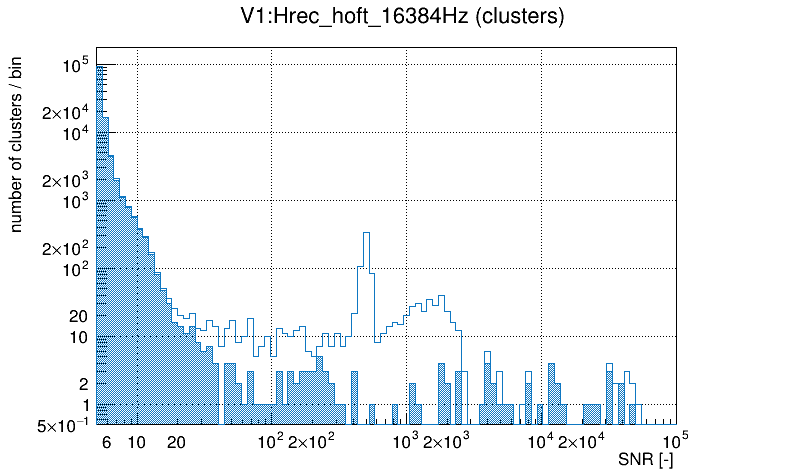

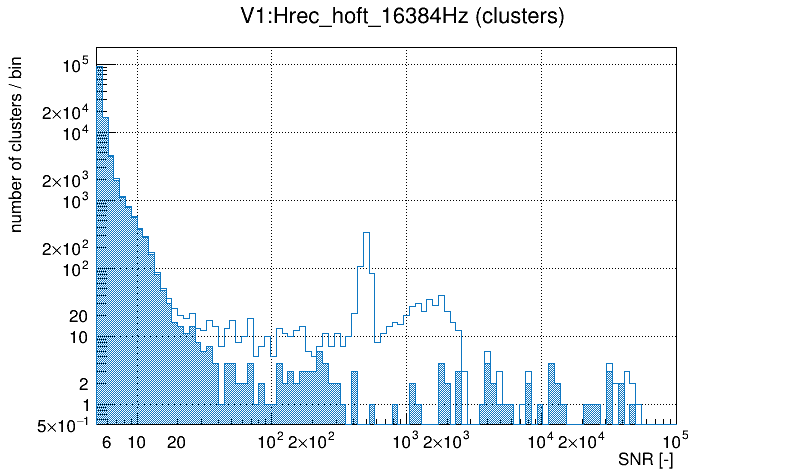

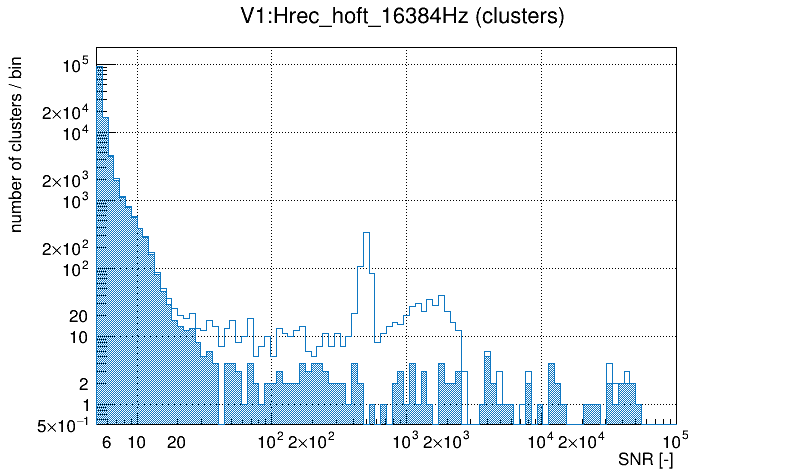

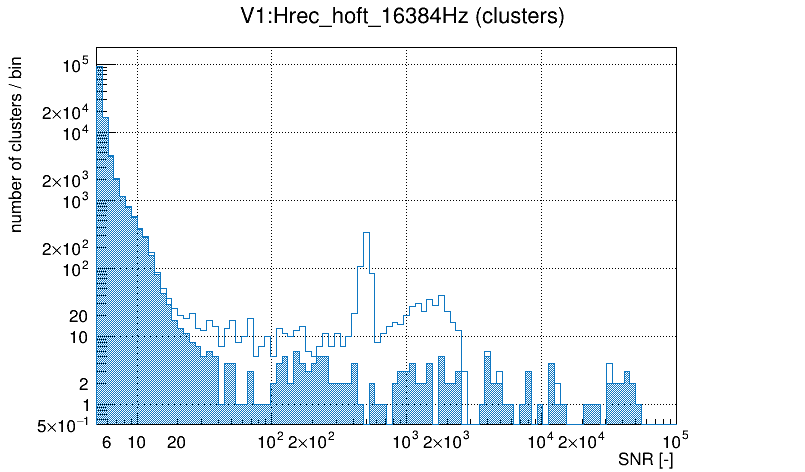

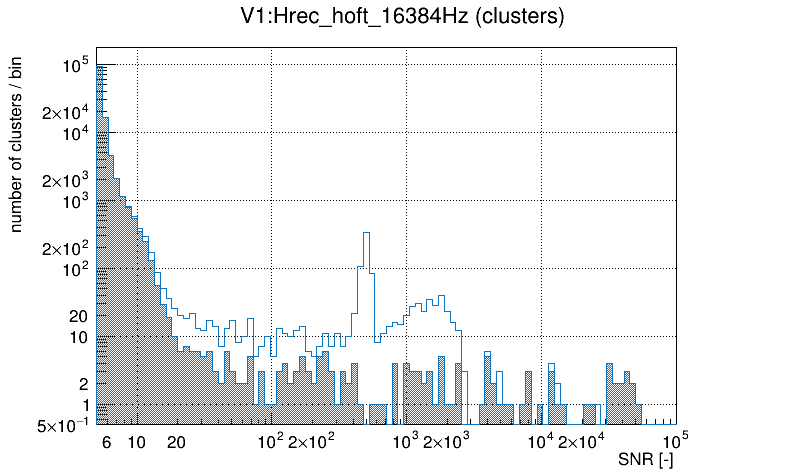

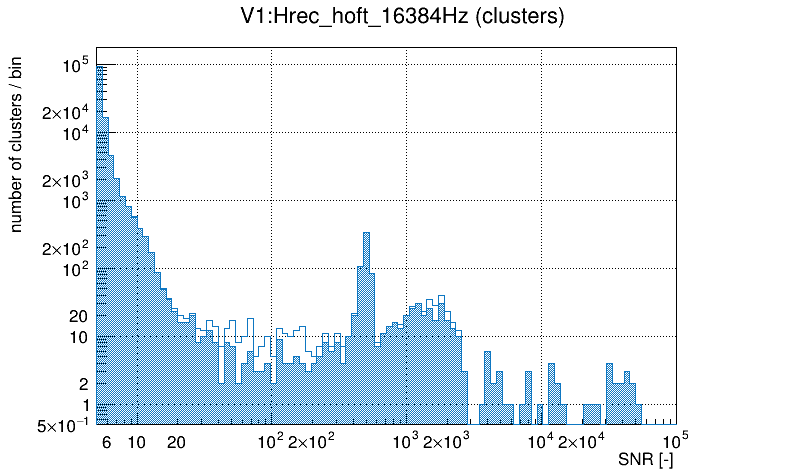

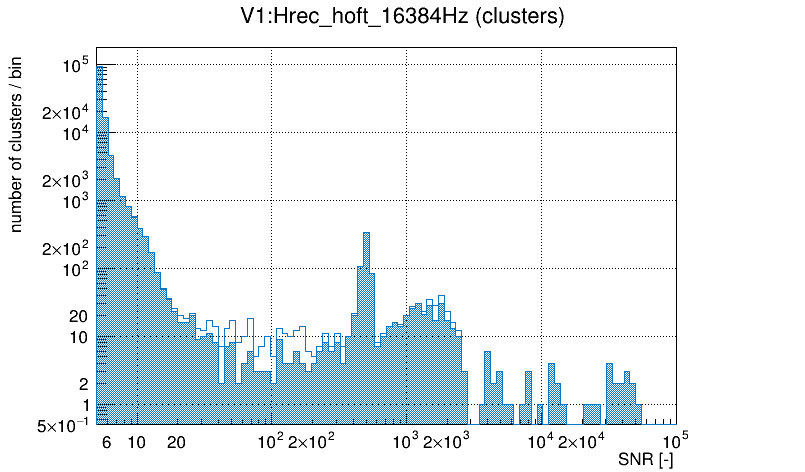

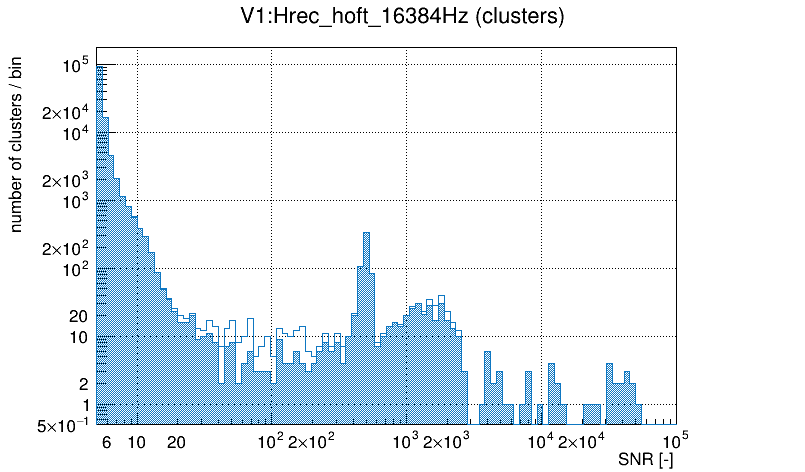

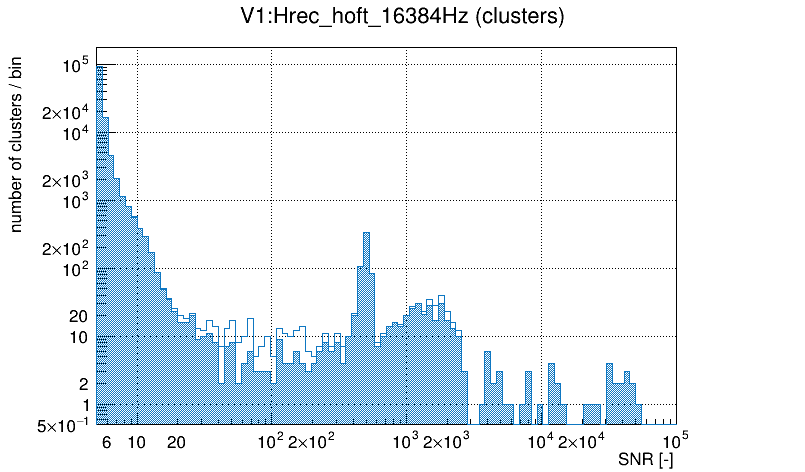

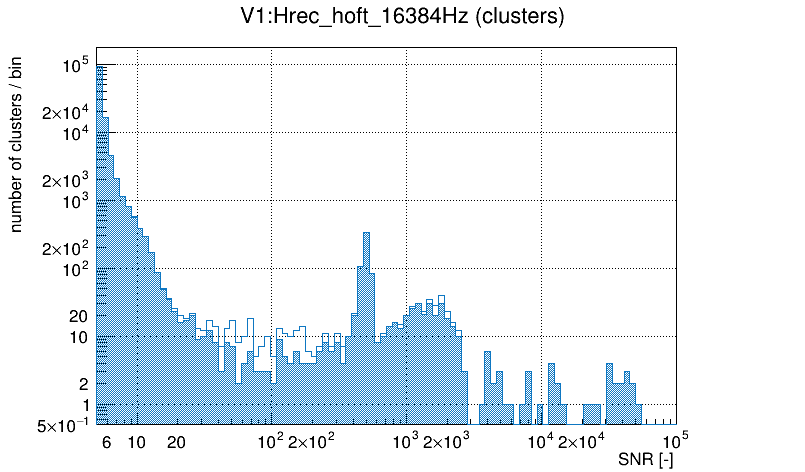

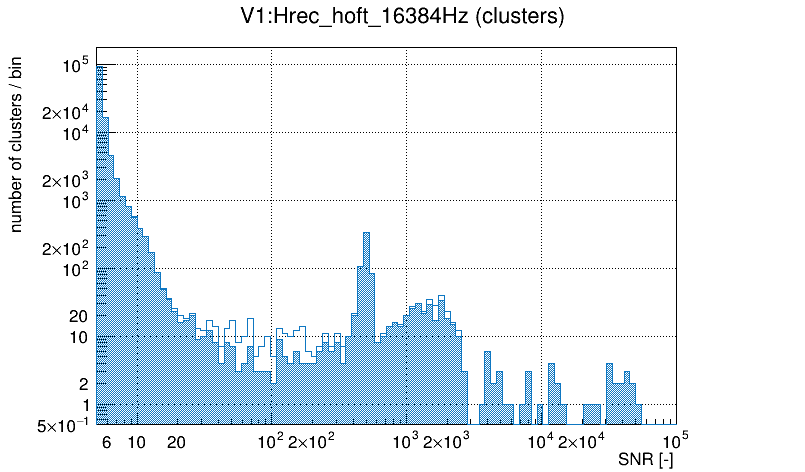

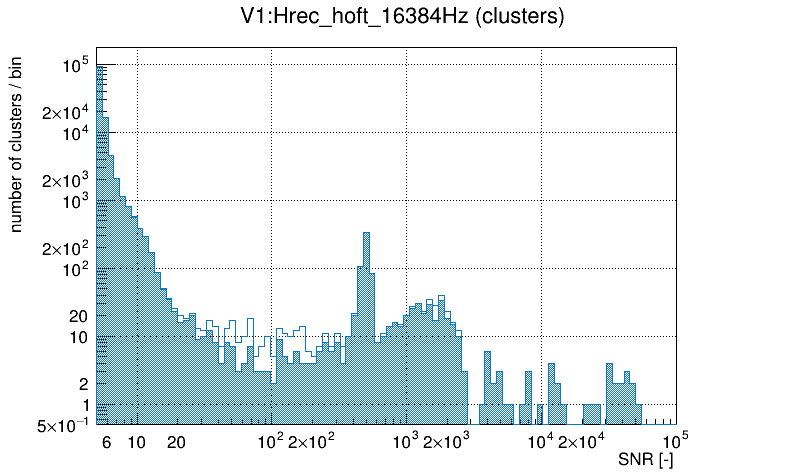

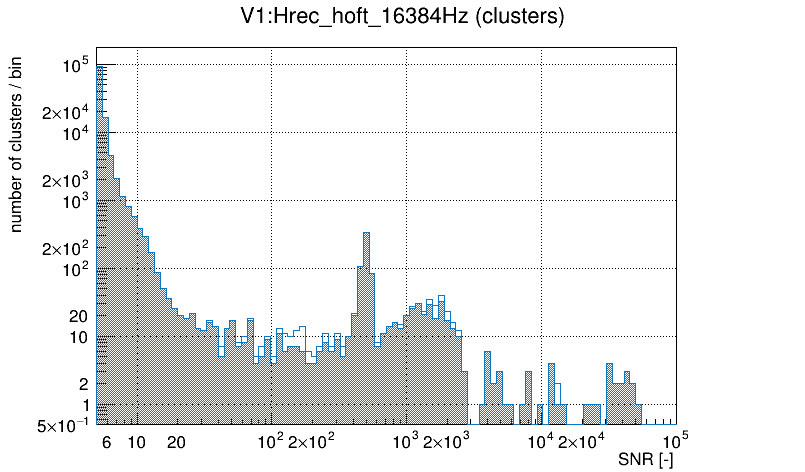

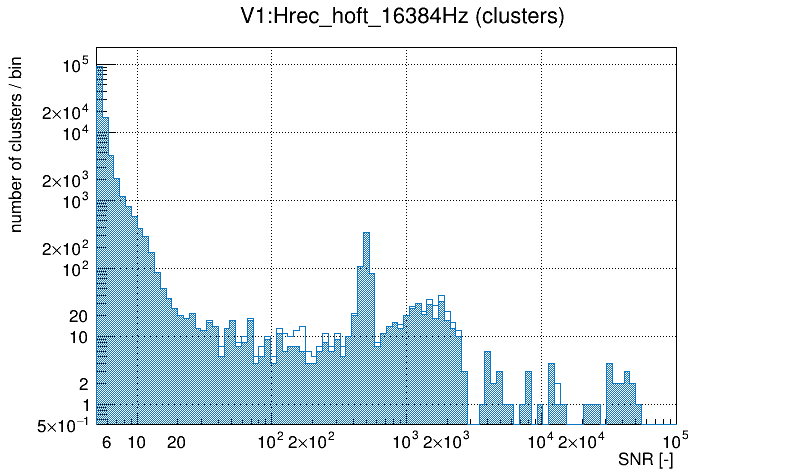

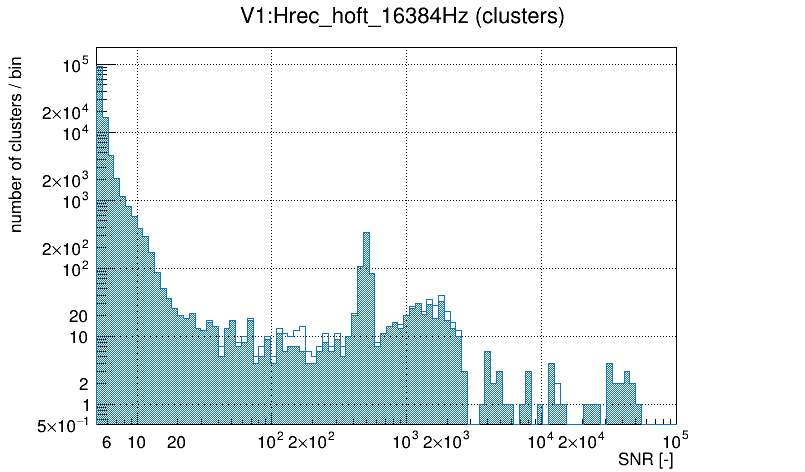

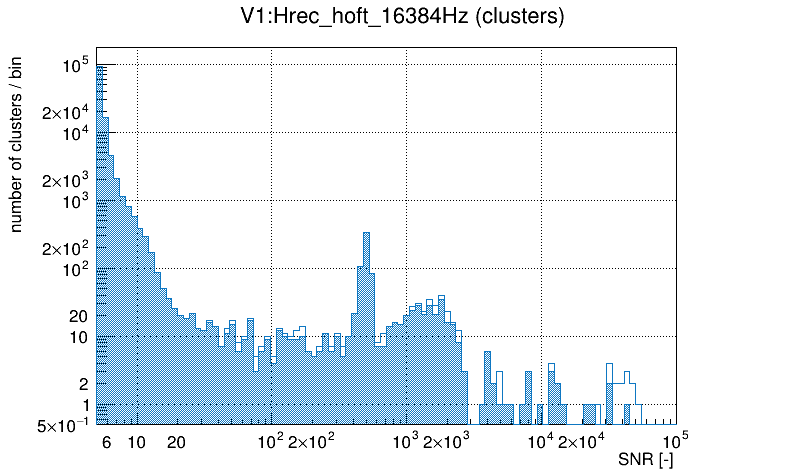

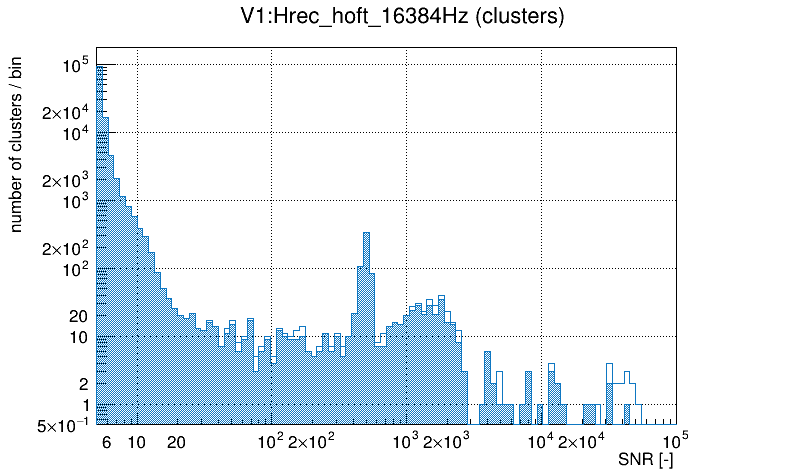

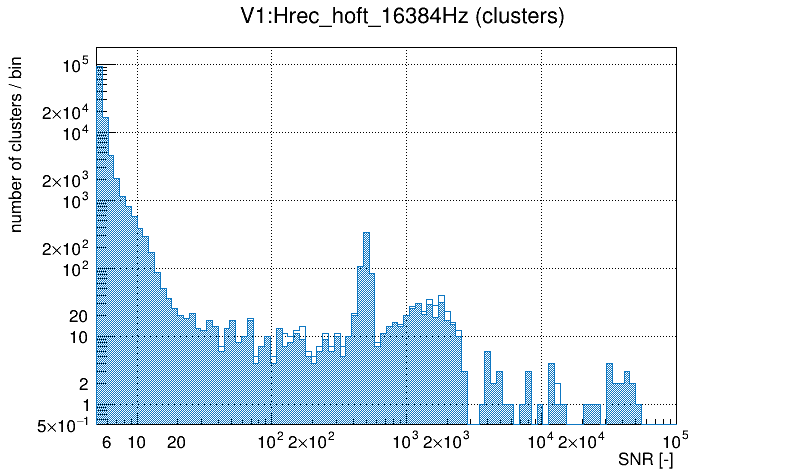

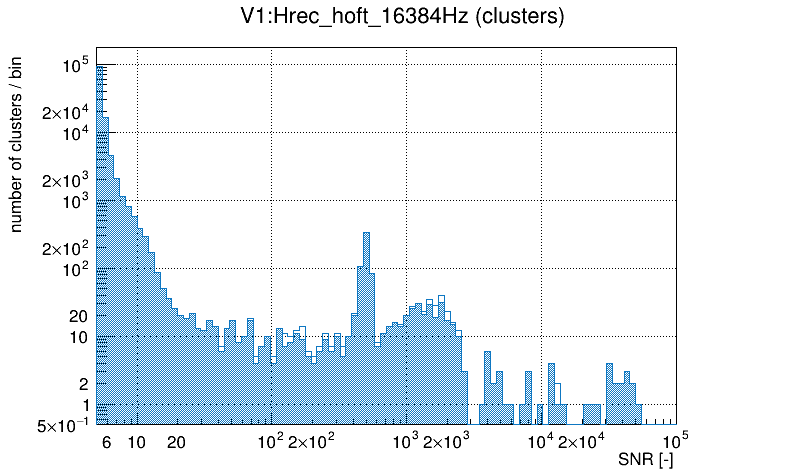

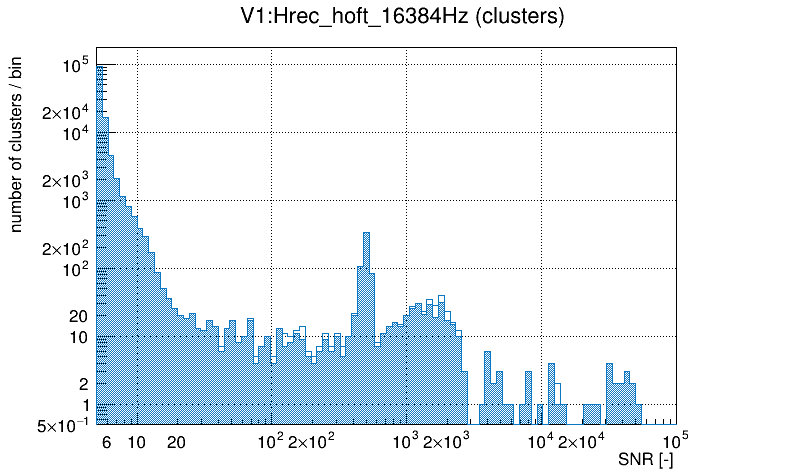

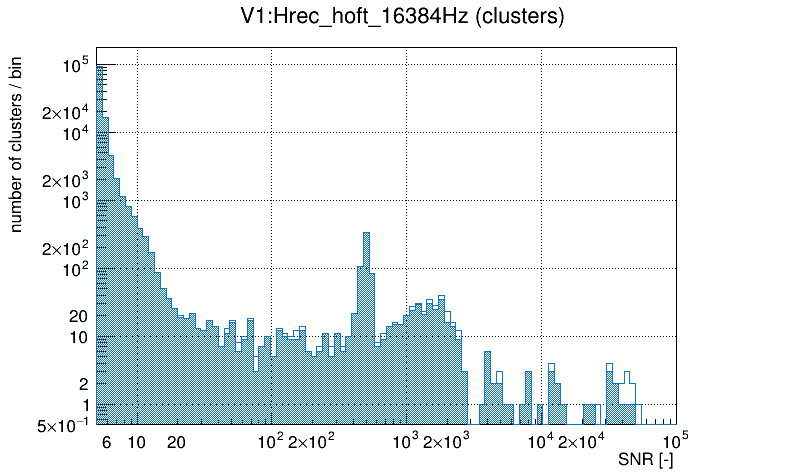

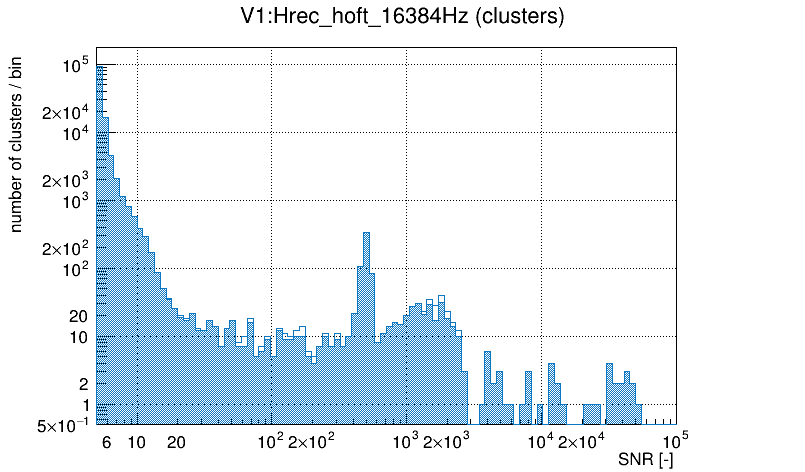

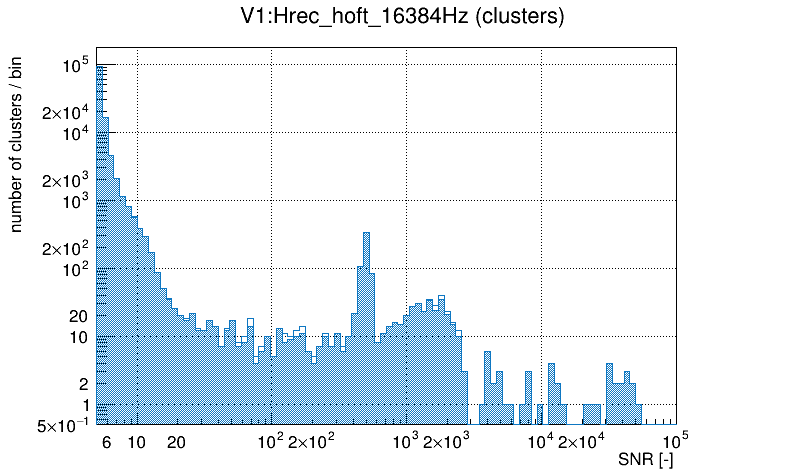

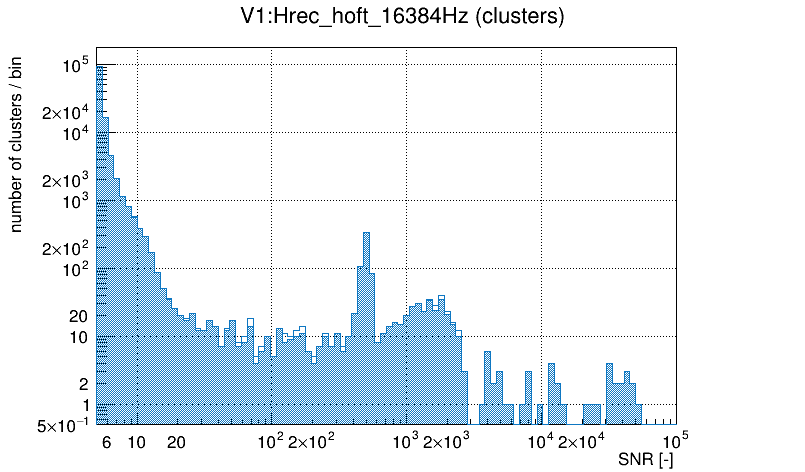

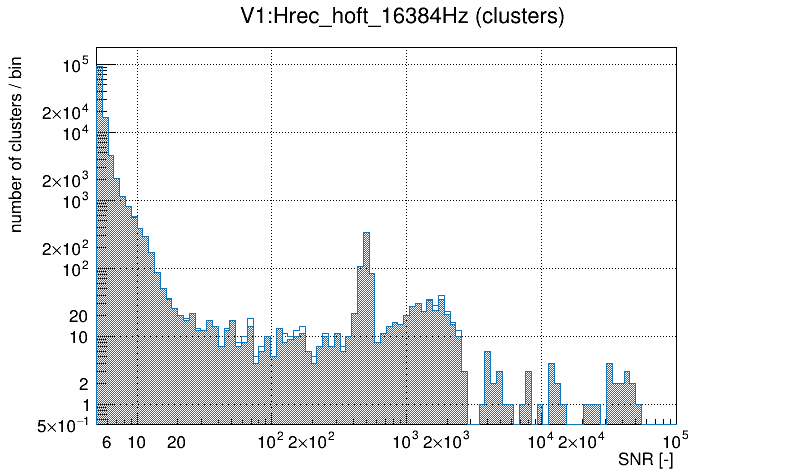

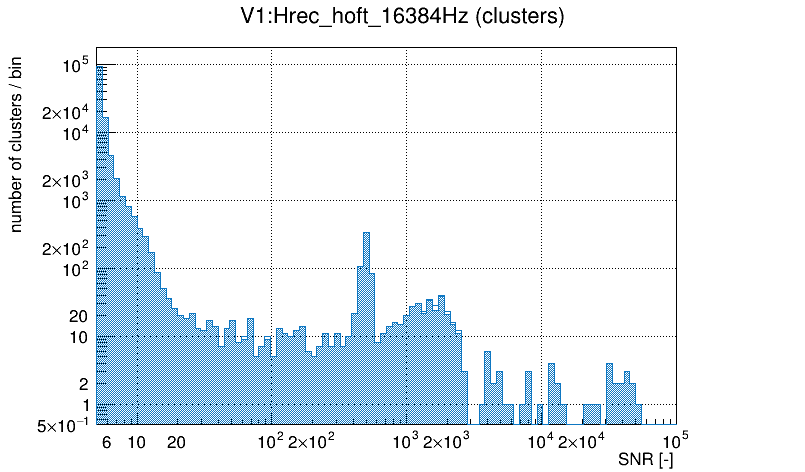

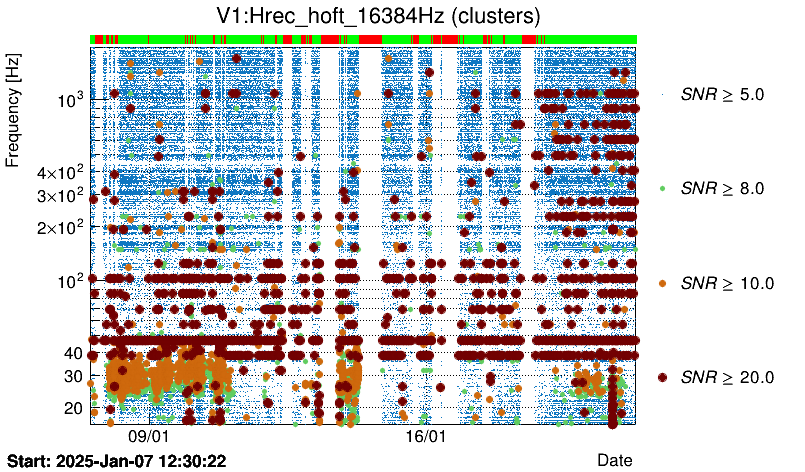

| V1:Hrec_hoft_16384Hz: 122170 clusters |

|---|

| V0 → V1:LSC_DARM_ERR_0, vetoed clusters: 8265 (6.765 %) |

| V1 → V1:LSC_DARM_INPUT_0, vetoed clusters: 8122 (6.648 %) |

| V2 → V1:LSC_DCP_DARM_CORR_FLT_LF_0, vetoed clusters: 7710 (6.311 %) |

| V3 → V1:LSC_DARM_CORR_raw_0, vetoed clusters: 7122 (5.830 %) |

| V4 → V1:LSC_DCP_DARM_ERR_FLT_HF_0, vetoed clusters: 7004 (5.733 %) |

| V5 → V1:LSC_DCP_DARM_ERR_FLT_HF_DEL_0, vetoed clusters: 6811 (5.575 %) |

| V6 → V1:LSC_DCP_DARM_ERR_FLT_LF_0, vetoed clusters: 6187 (5.064 %) |

| V7 → V1:LSC_DCP_DARM_ERR_FLT_LF_DEL_0, vetoed clusters: 6099 (4.992 %) |

| V8 → V1:LSC_DCP_MM_RE_0, vetoed clusters: 1969 (1.612 %) |

| V9 → V1:LSC_NE_CORR_0, vetoed clusters: 1648 (1.349 %) |