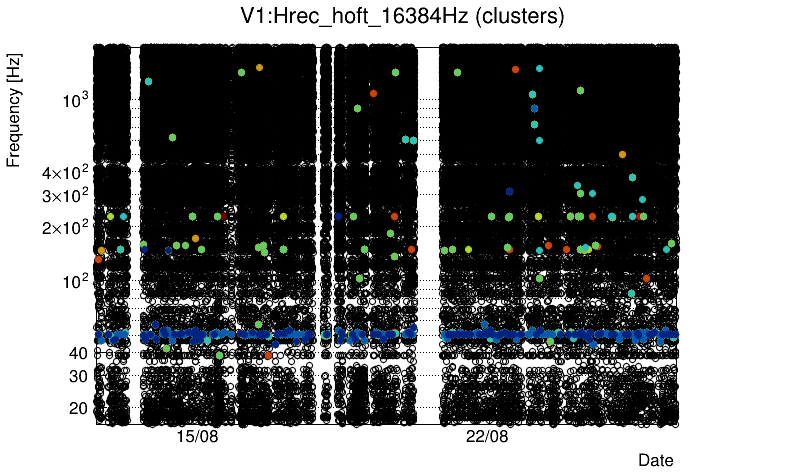

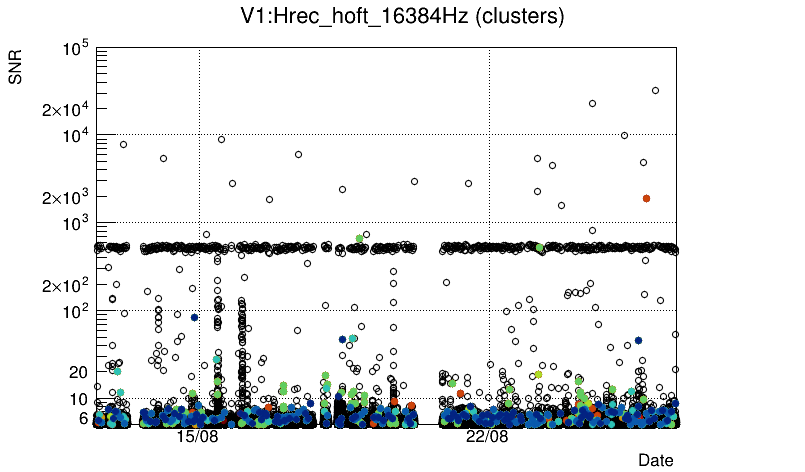

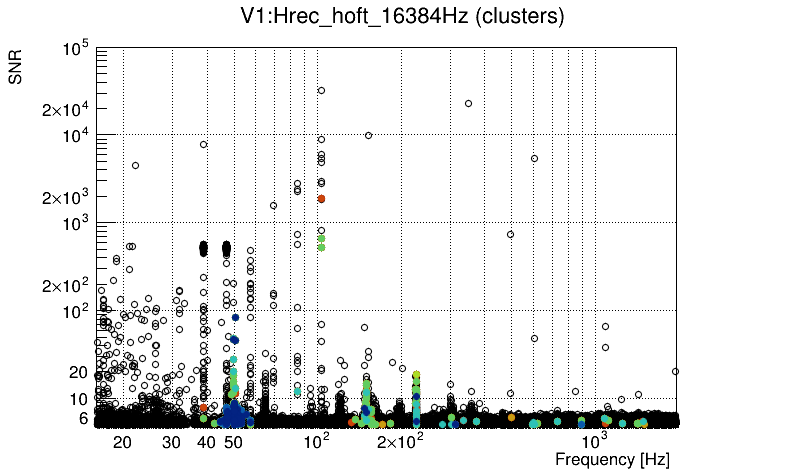

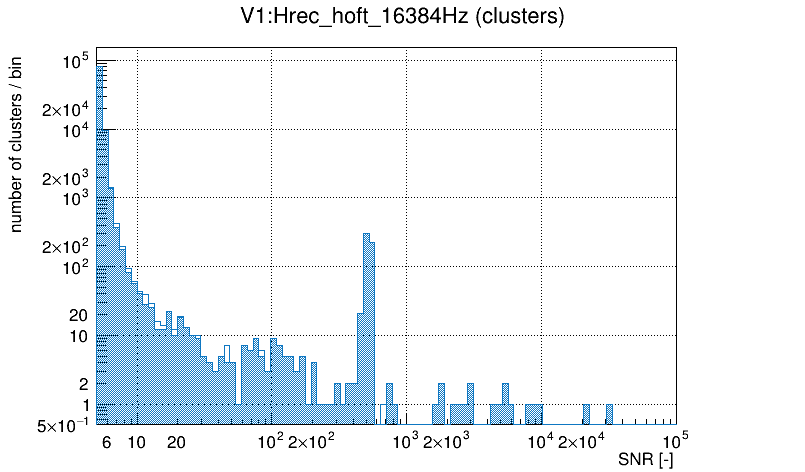

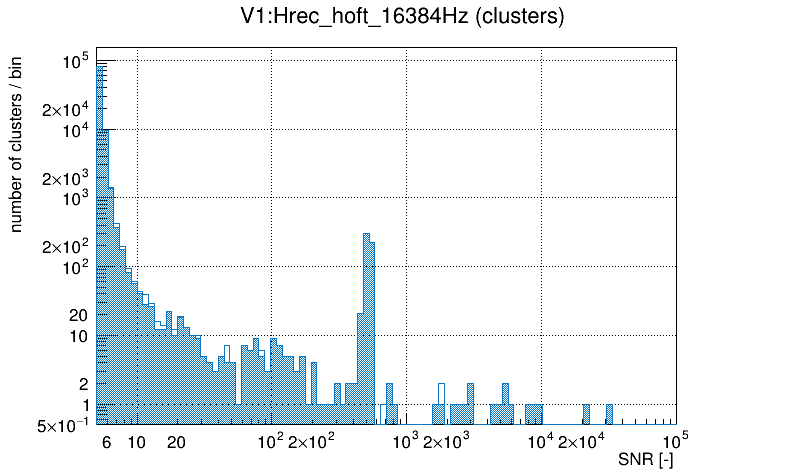

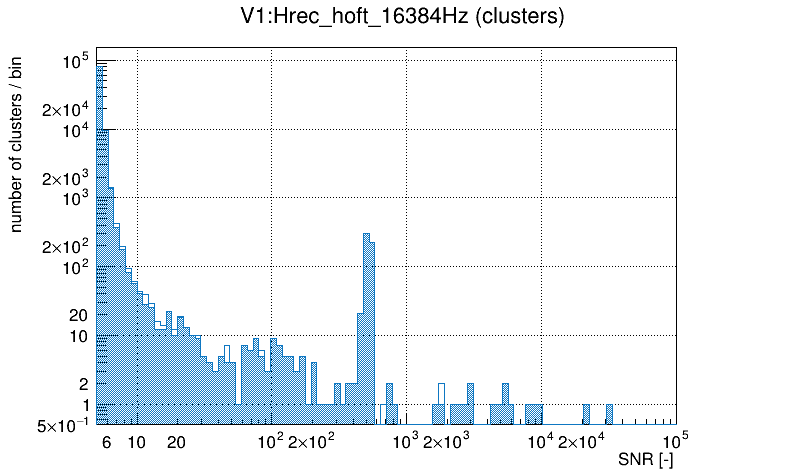

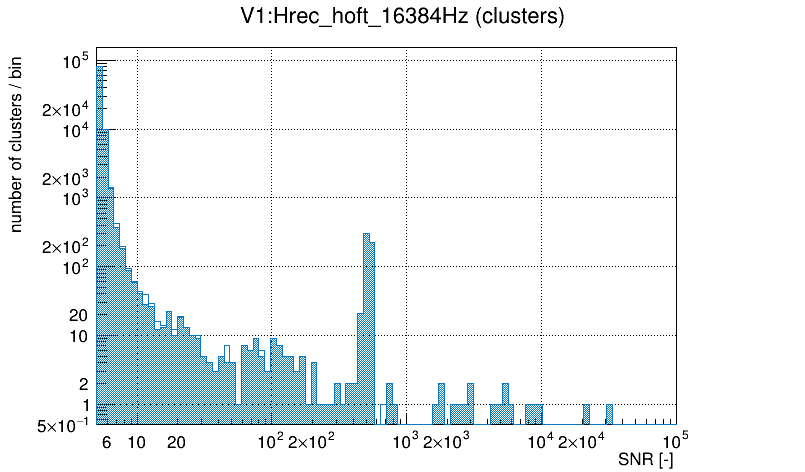

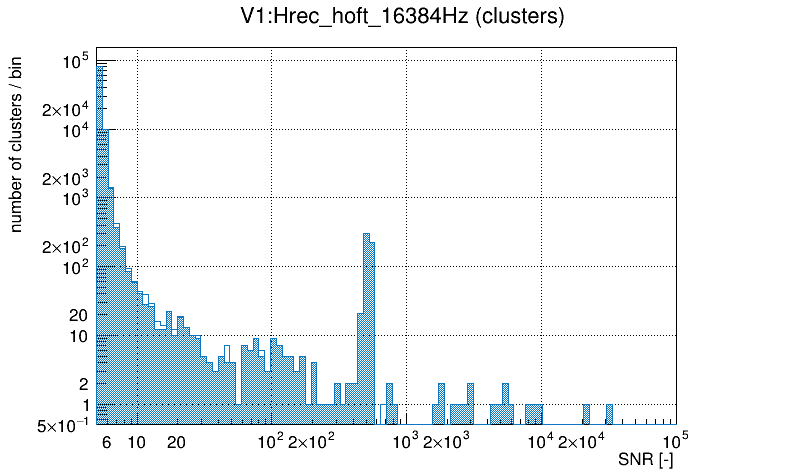

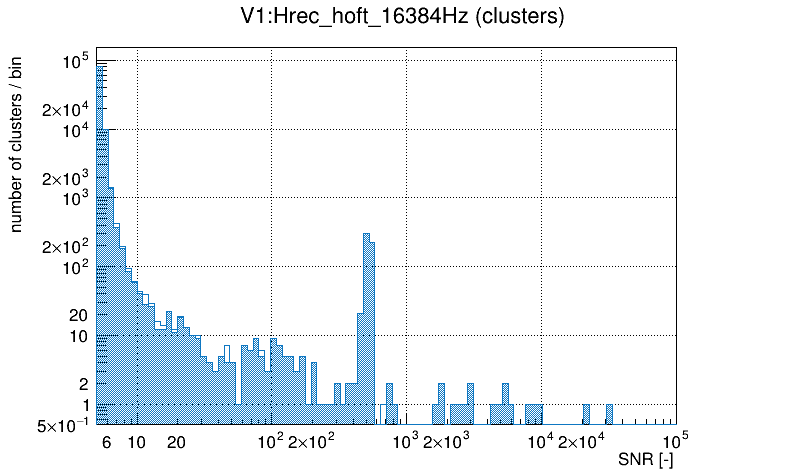

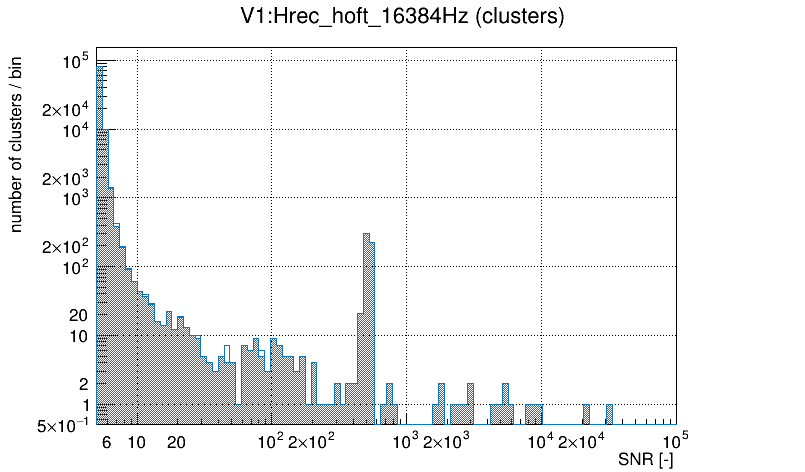

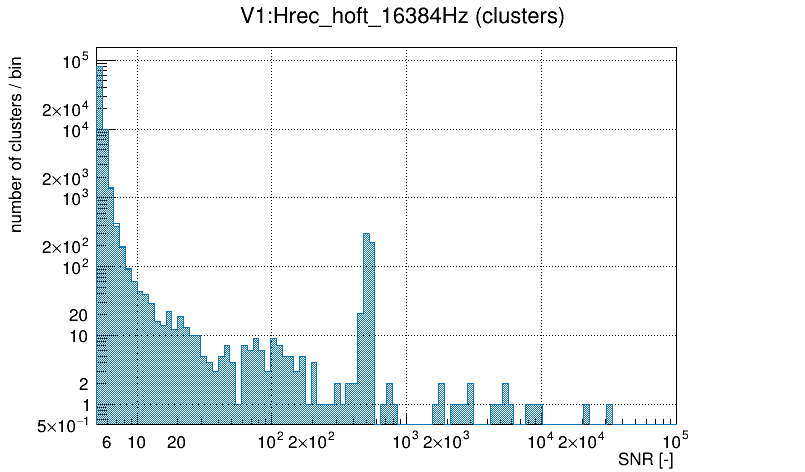

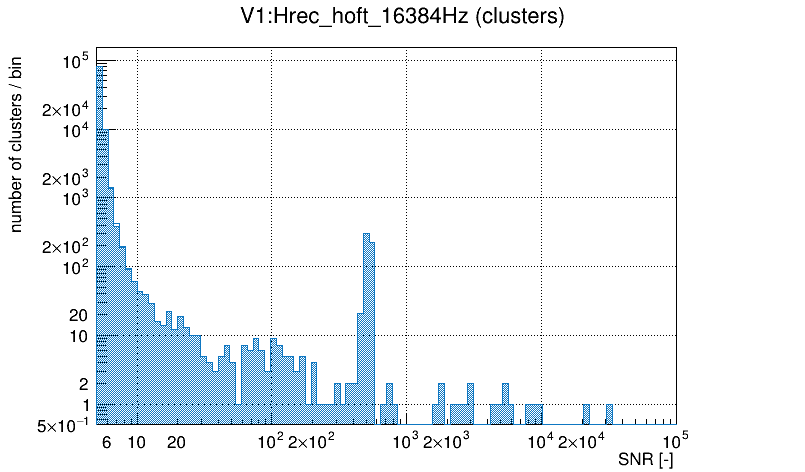

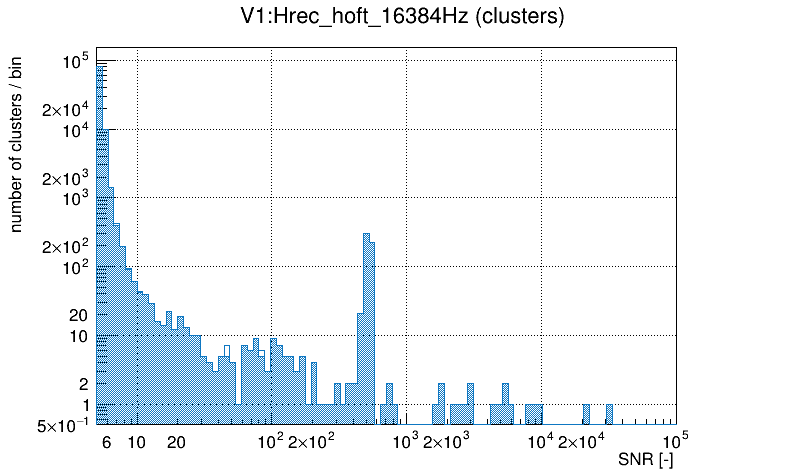

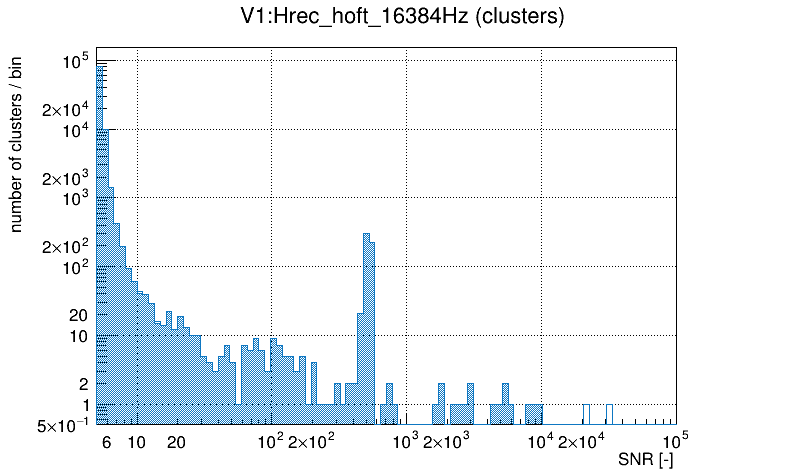

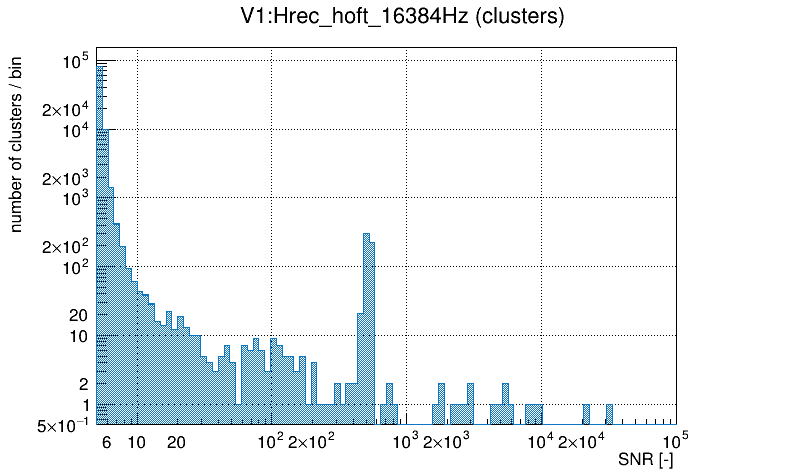

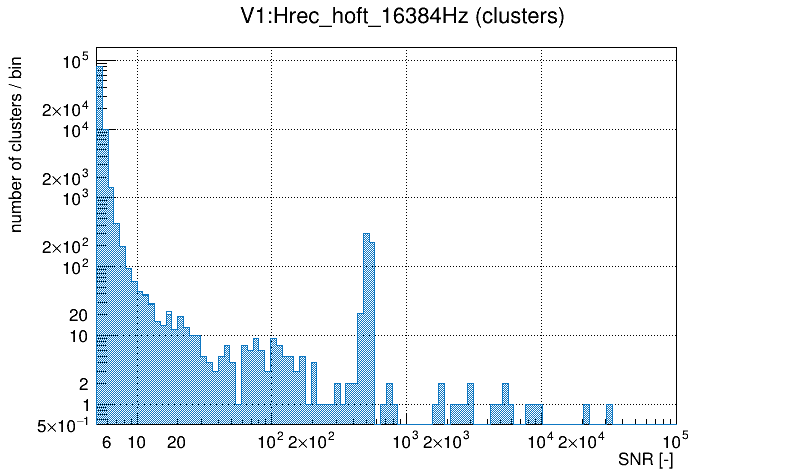

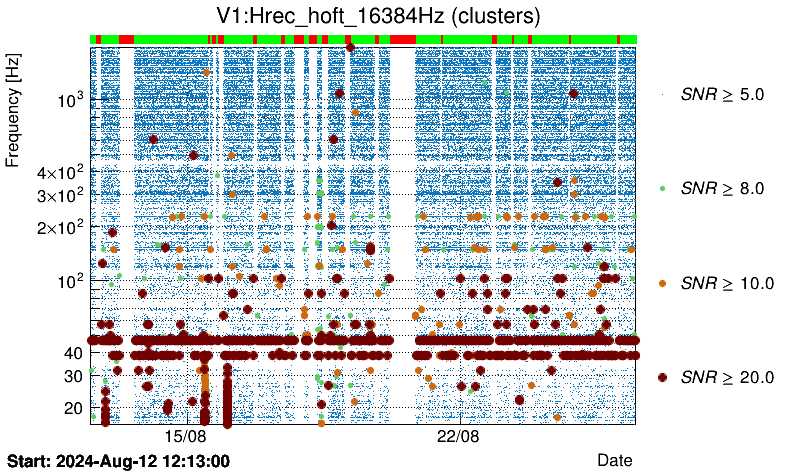

| V1:Hrec_hoft_16384Hz: 94622 clusters |

|---|

| V0 → V1:SIB2_B2_PD3_Audio_ool_0, vetoed clusters: 333 (0.352 %) |

| V1 → V1:SIB2_B2_PD3_Blended_0, vetoed clusters: 331 (0.350 %) |

| V2 → V1:SIB2_B2_PD3_Audio_0, vetoed clusters: 331 (0.350 %) |

| V3 → V1:SIB2_B2_PD2_Blended_0, vetoed clusters: 274 (0.290 %) |

| V4 → V1:SIB2_B2_PD2_Audio_ool_0, vetoed clusters: 274 (0.290 %) |

| V5 → V1:SIB2_B2_PD2_Audio_0, vetoed clusters: 269 (0.284 %) |

| V6 → V1:SIB2_B2_PD2_DC_0, vetoed clusters: 218 (0.230 %) |

| V7 → V1:SIB2_B2_QD1_H_0, vetoed clusters: 190 (0.201 %) |

| V8 → V1:SIB2_B2_QD1_H_norm_0, vetoed clusters: 184 (0.194 %) |

| V9 → V1:SIB2_B2_PD3_DC_0, vetoed clusters: 111 (0.117 %) |