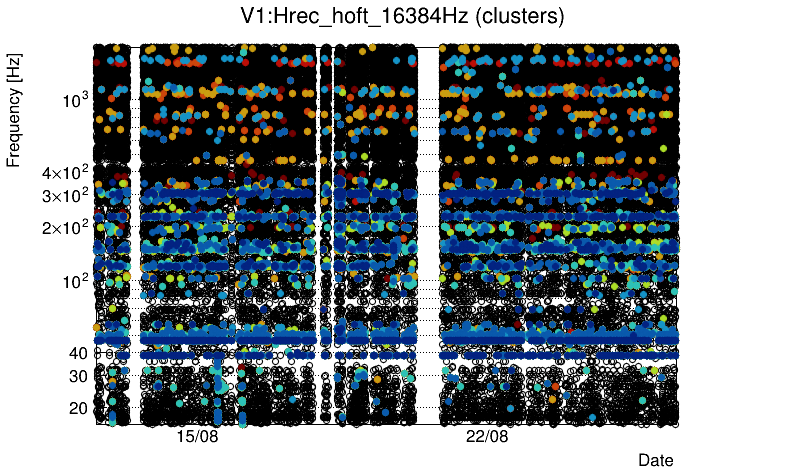

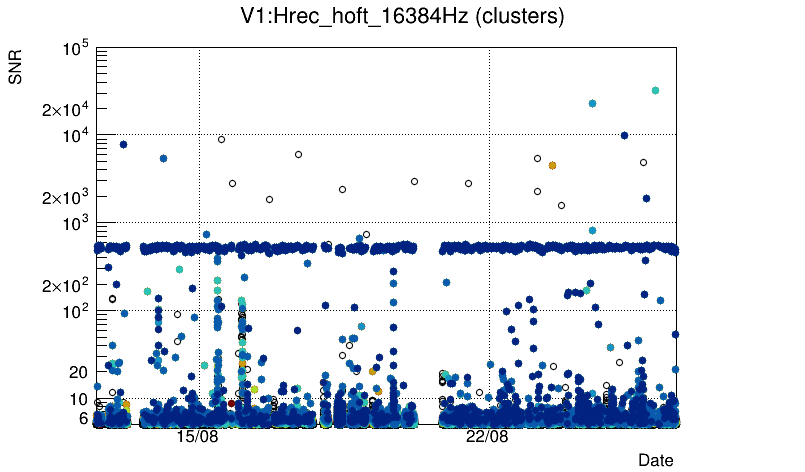

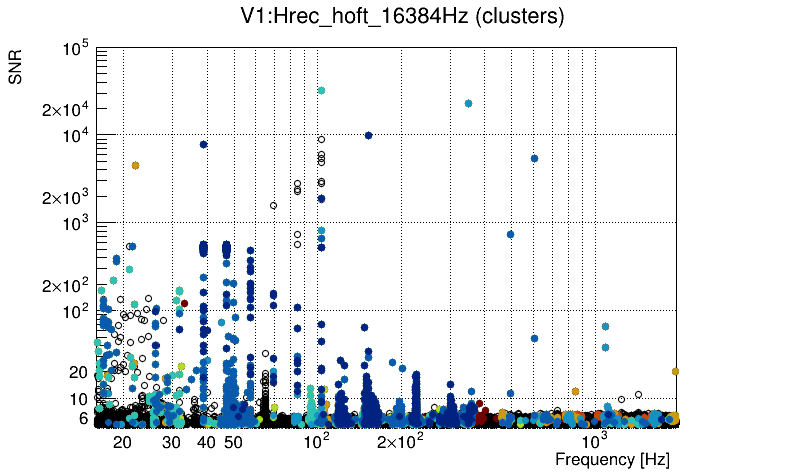

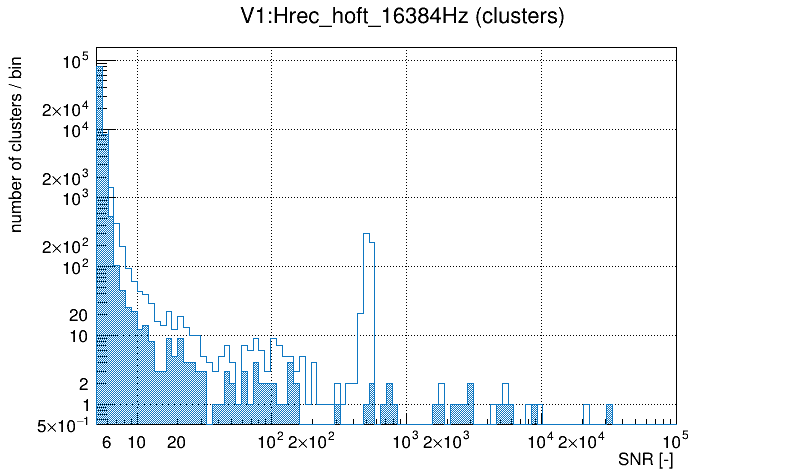

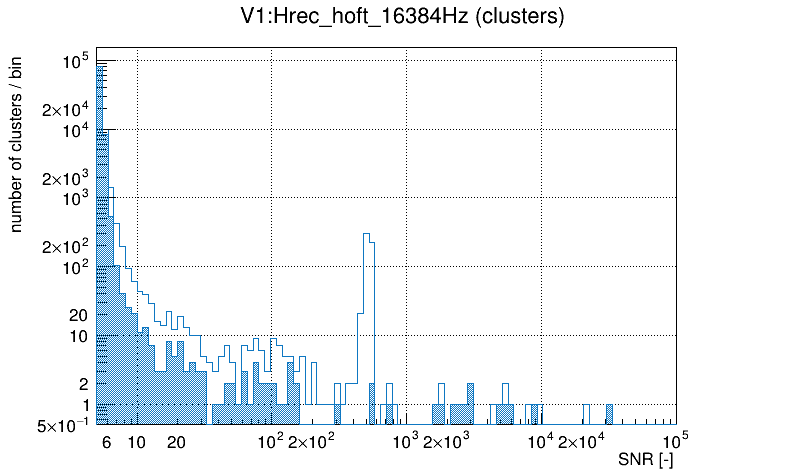

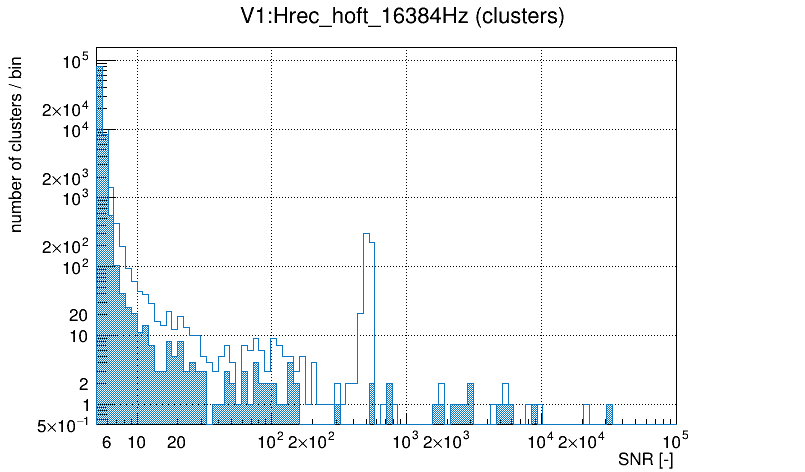

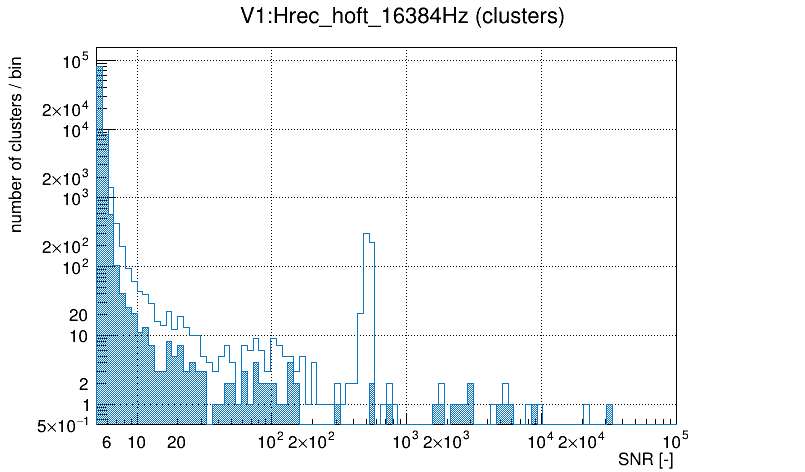

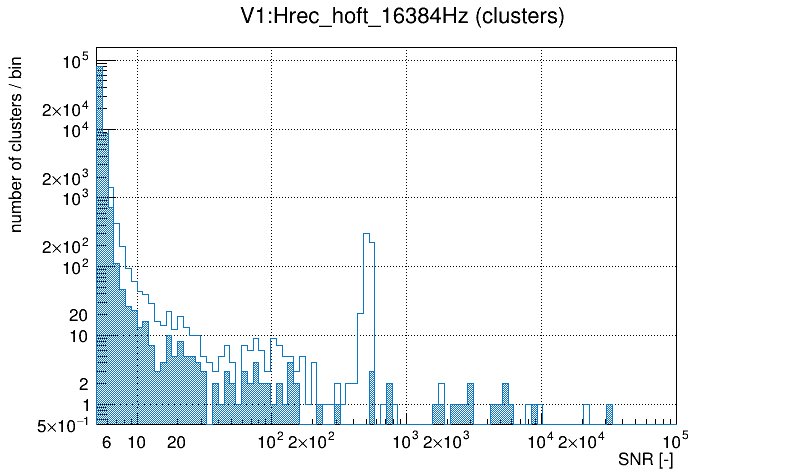

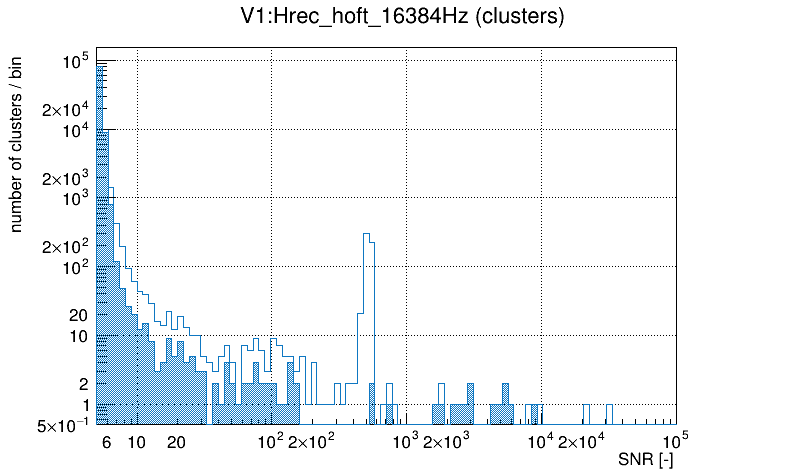

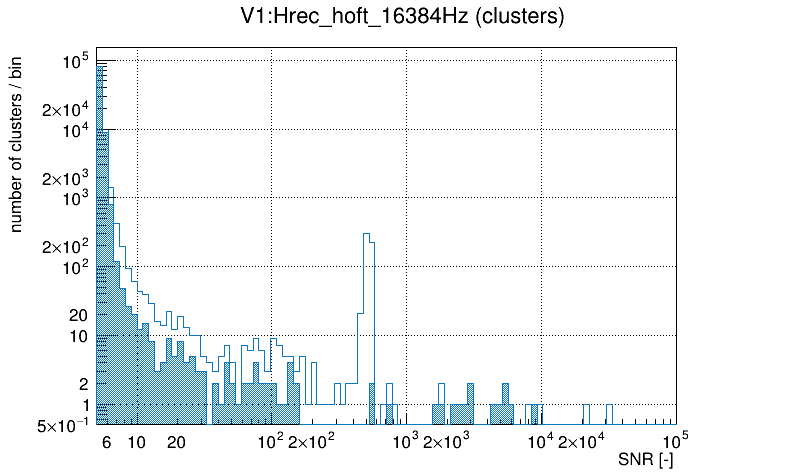

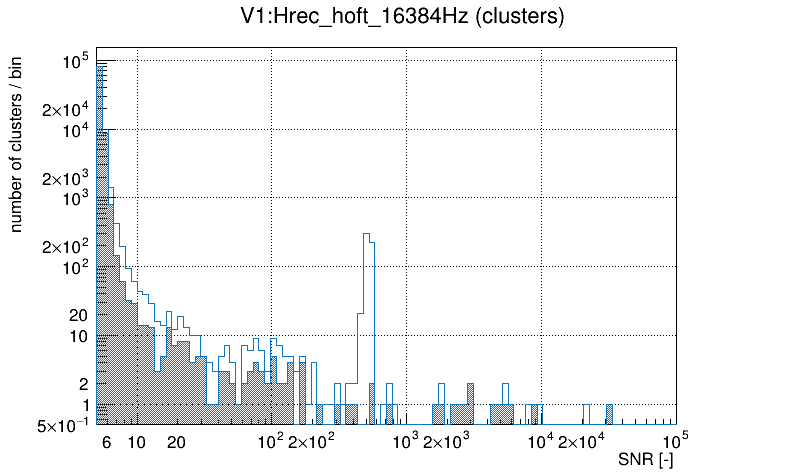

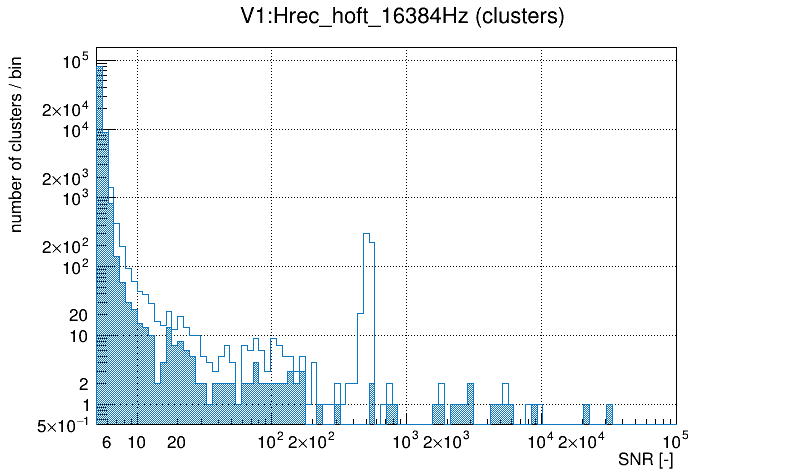

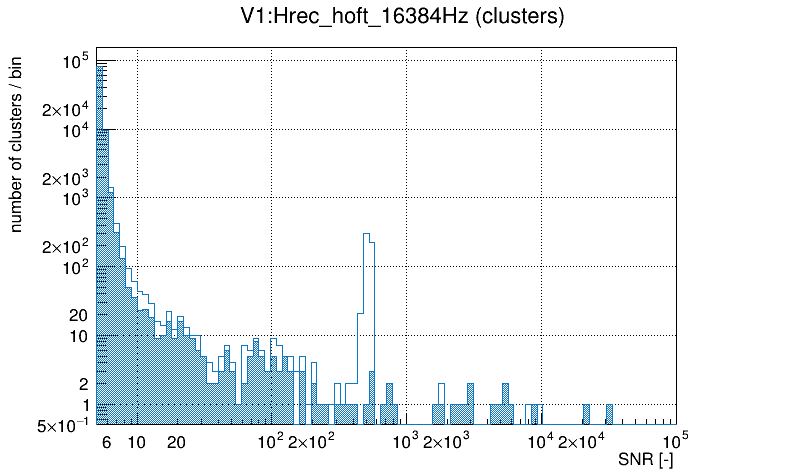

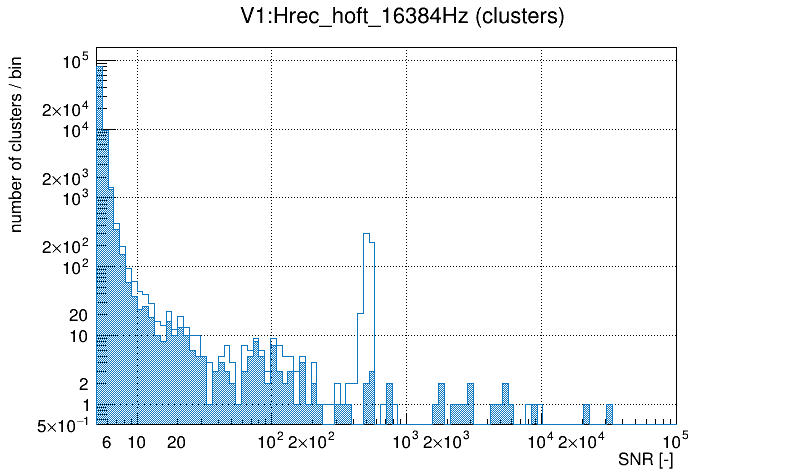

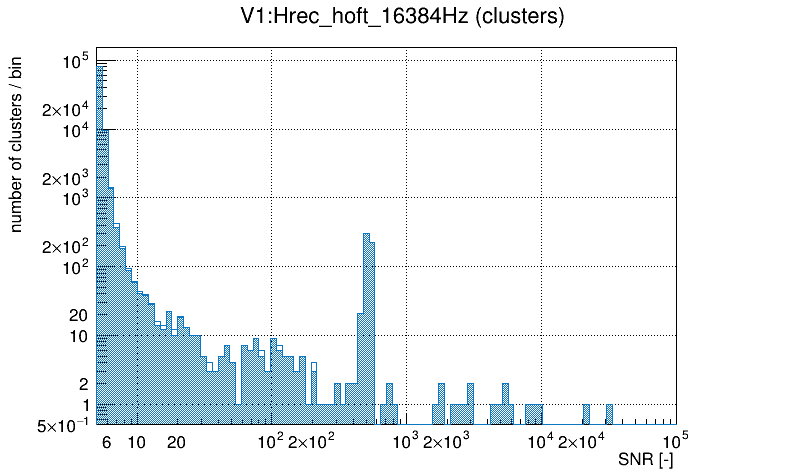

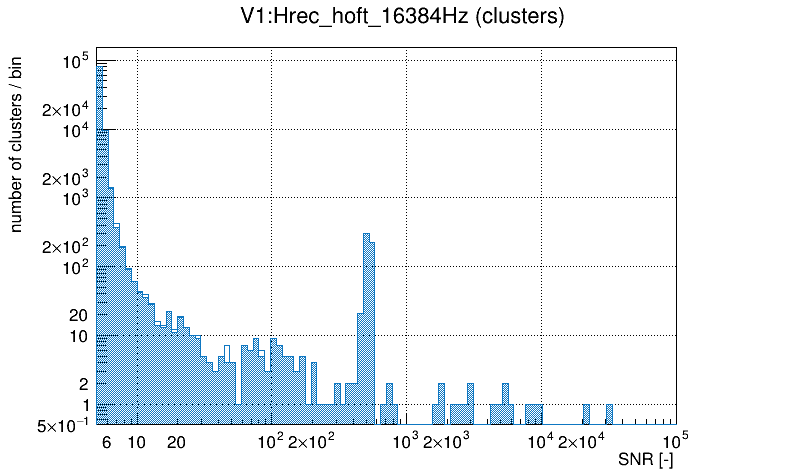

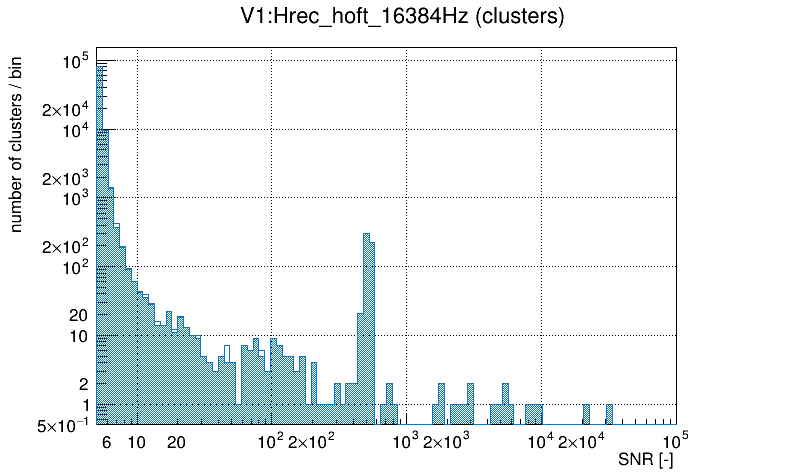

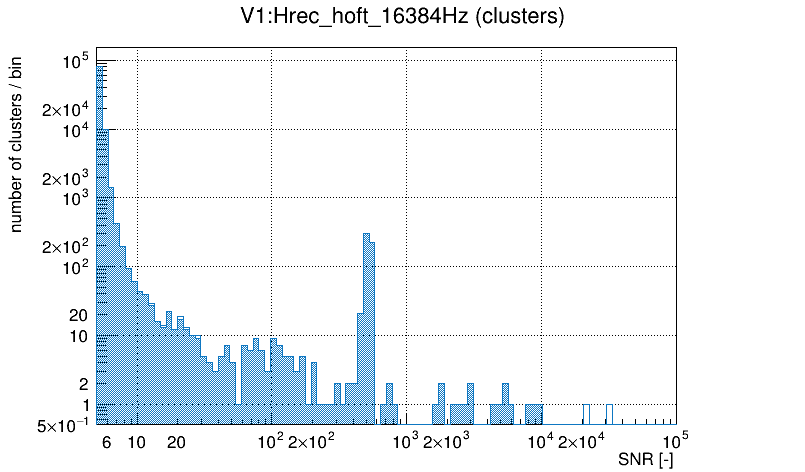

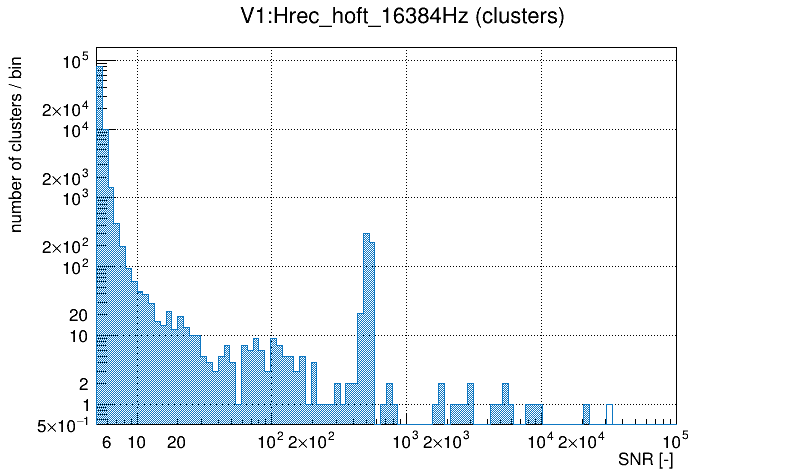

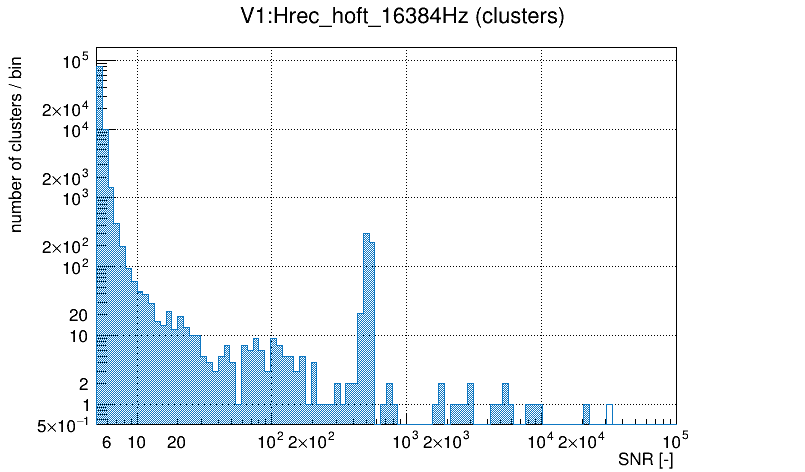

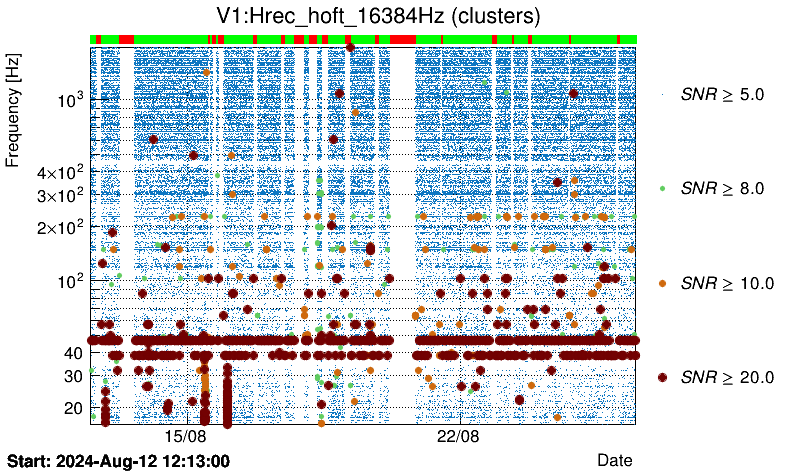

| V1:Hrec_hoft_16384Hz: 94622 clusters |

|---|

| V0 → V1:LSC_DARM_0, vetoed clusters: 4215 (4.455 %) |

| V1 → V1:LSC_DARM_ERR_0, vetoed clusters: 4059 (4.290 %) |

| V2 → V1:LSC_B1_DC_0, vetoed clusters: 4009 (4.237 %) |

| V3 → V1:LSC_B1_DC_IN1_0, vetoed clusters: 3967 (4.192 %) |

| V4 → V1:LSC_DARM_INPUT_0, vetoed clusters: 3691 (3.901 %) |

| V5 → V1:LSC_B1_DC_IN2_0, vetoed clusters: 3531 (3.732 %) |

| V6 → V1:LSC_B1_DC_INPUT_0, vetoed clusters: 3531 (3.732 %) |

| V7 → V1:LSC_DARM_CORR_raw_0, vetoed clusters: 3309 (3.497 %) |

| V8 → V1:LSC_DCP_DARM_CORR_FLT_LF_0, vetoed clusters: 3099 (3.275 %) |

| V9 → V1:LSC_DCP_DARM_CORR_FLT_HF_0, vetoed clusters: 1469 (1.552 %) |