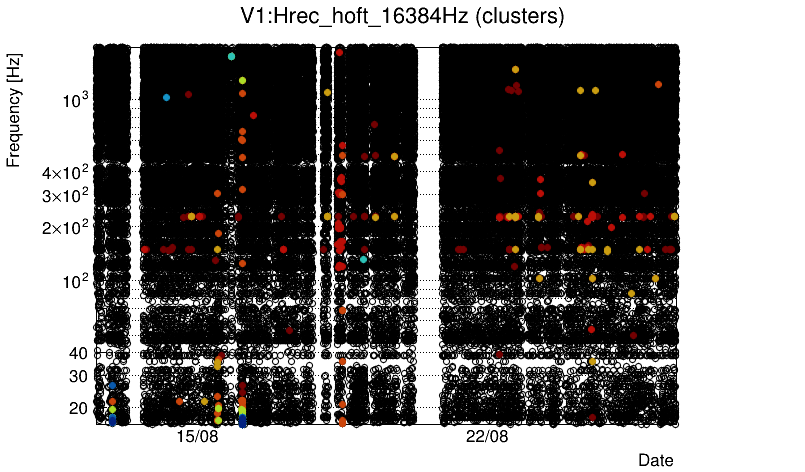

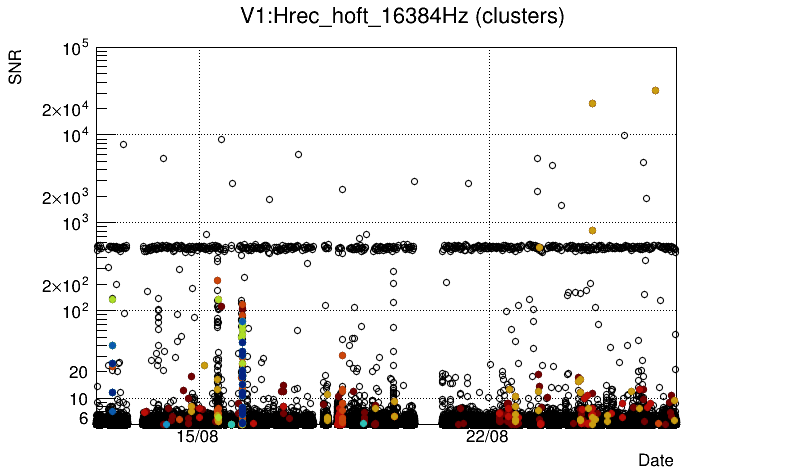

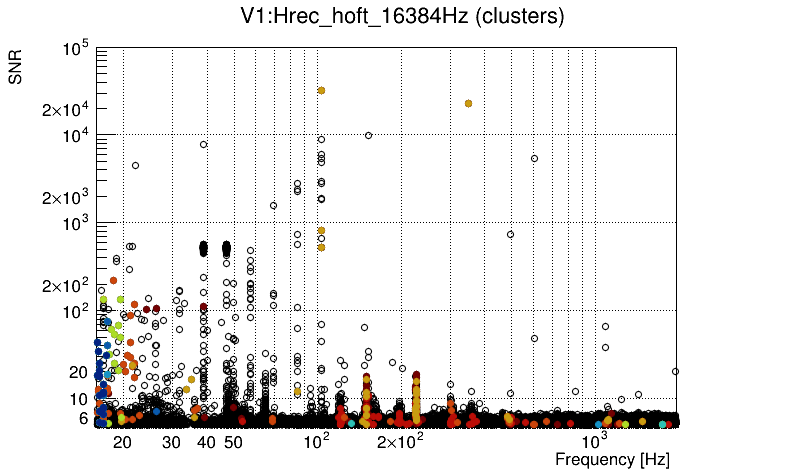

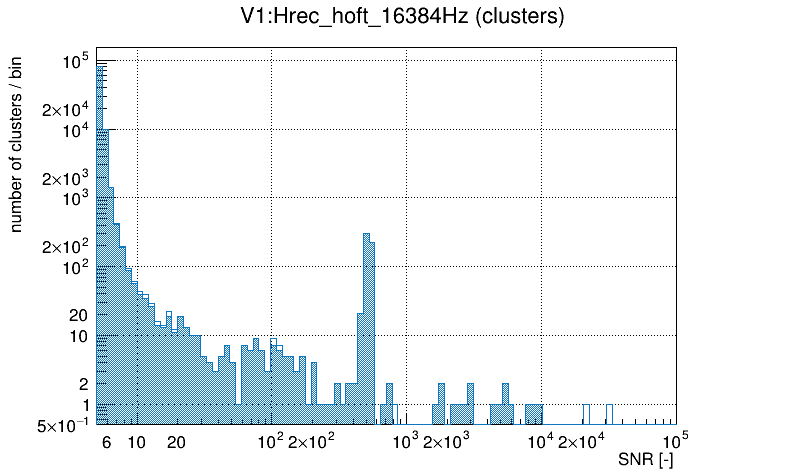

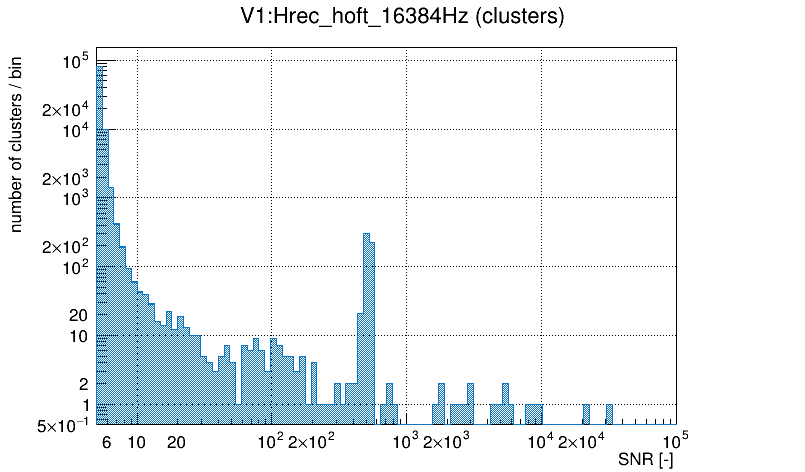

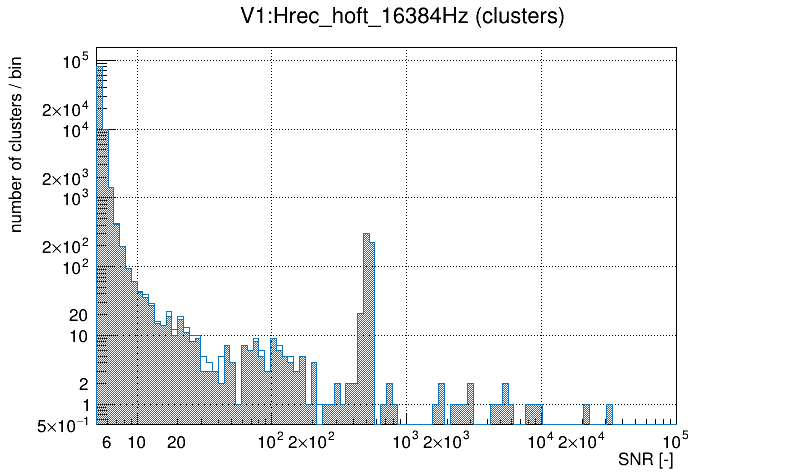

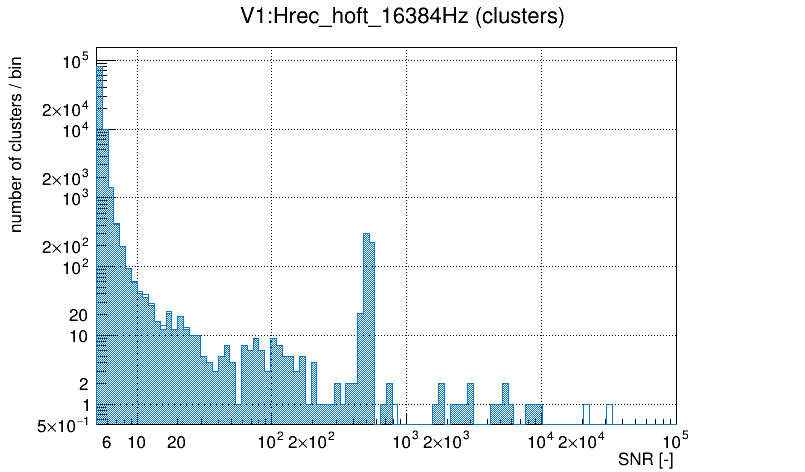

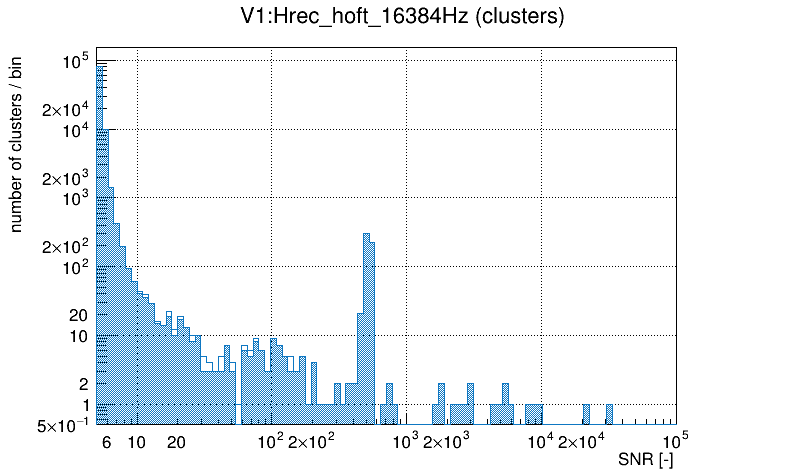

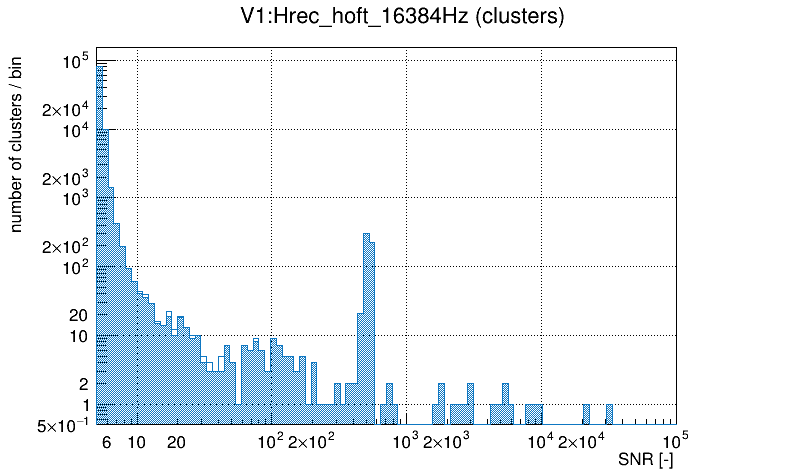

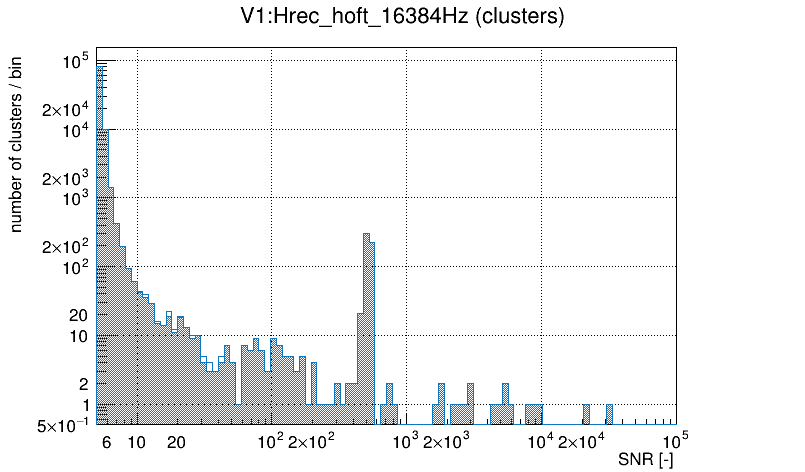

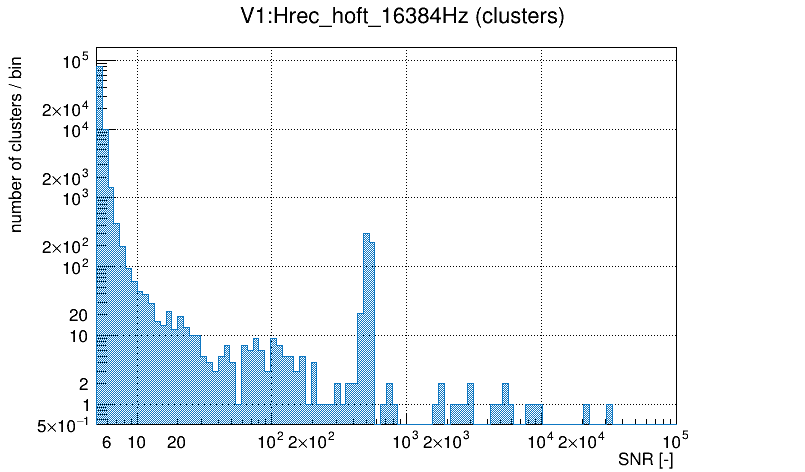

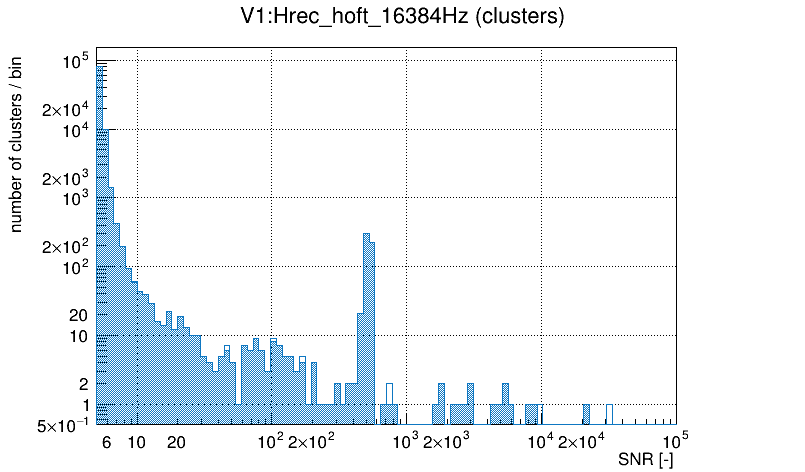

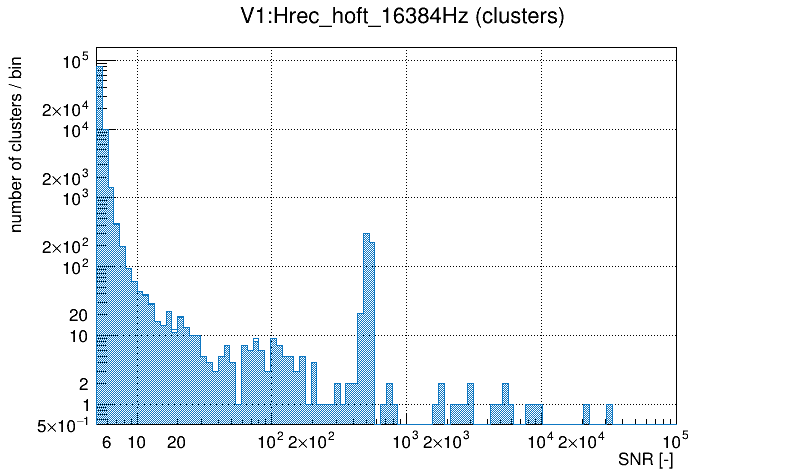

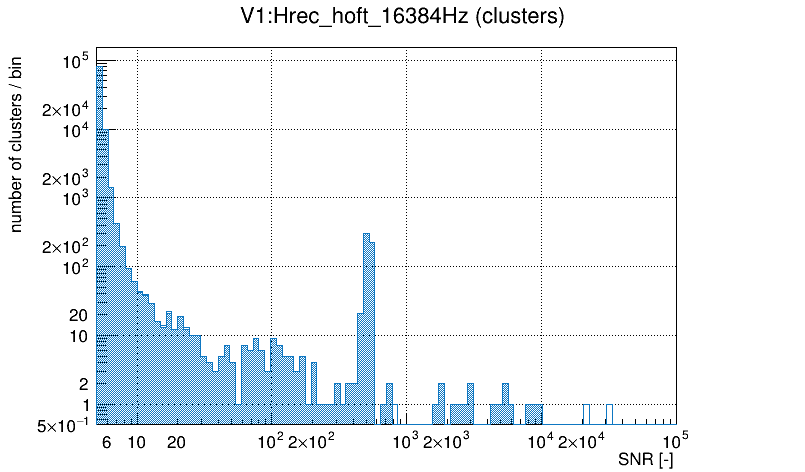

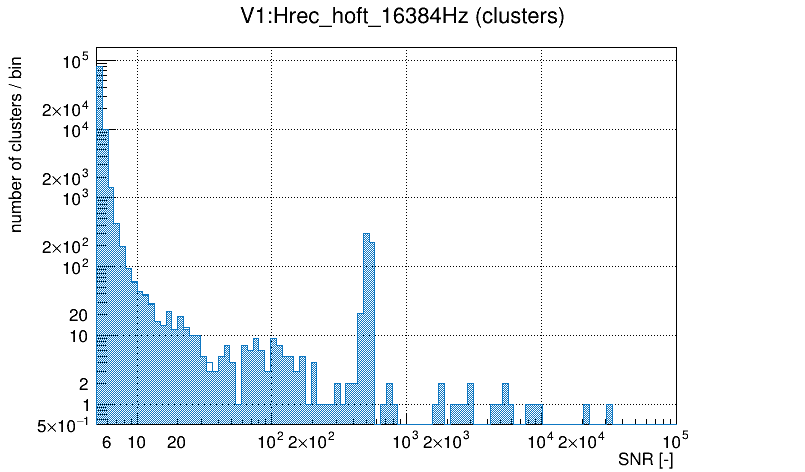

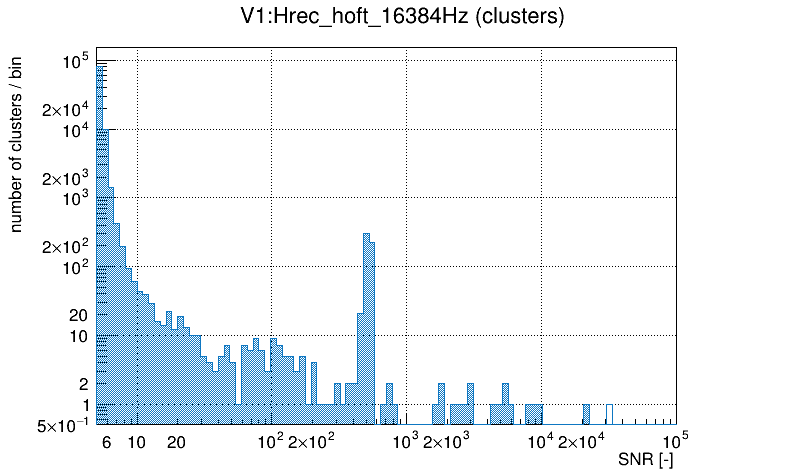

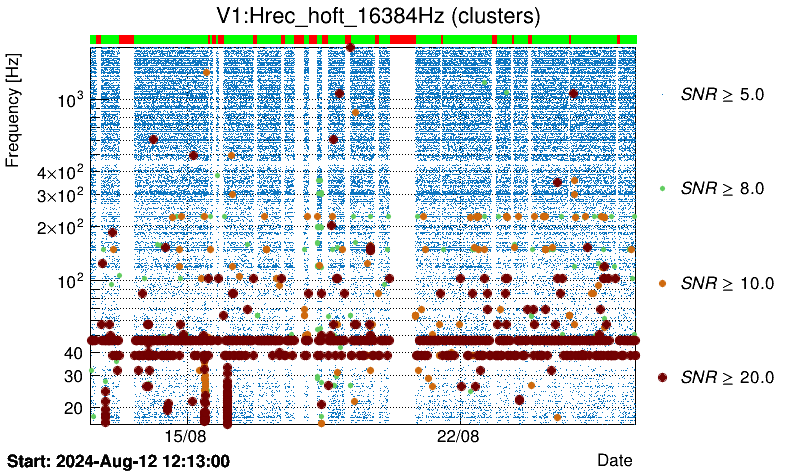

| V1:Hrec_hoft_16384Hz: 94622 clusters |

|---|

| V0 → V1:ASC_B4_QD1_H_0, vetoed clusters: 102 (0.108 %) |

| V1 → V1:ASC_BS_B1p_TY_HF_0, vetoed clusters: 76 (0.080 %) |

| V2 → V1:ASC_B7B8_QD1_SUM_H_0, vetoed clusters: 64 (0.068 %) |

| V3 → V1:ASC_B5_QD2_56MHz_V_I_0, vetoed clusters: 41 (0.043 %) |

| V4 → V1:ASC_B7_QD2_Sum_0, vetoed clusters: 37 (0.039 %) |

| V5 → V1:ASC_B7_QD1_Sum_0, vetoed clusters: 25 (0.026 %) |

| V6 → V1:ASC_B7_QD2_H_0, vetoed clusters: 24 (0.025 %) |

| V7 → V1:ASC_B7_QD2_V_0, vetoed clusters: 22 (0.023 %) |

| V8 → V1:ASC_B7_QD1_V_0, vetoed clusters: 22 (0.023 %) |

| V9 → V1:ASC_B7_QD1_H_0, vetoed clusters: 20 (0.021 %) |