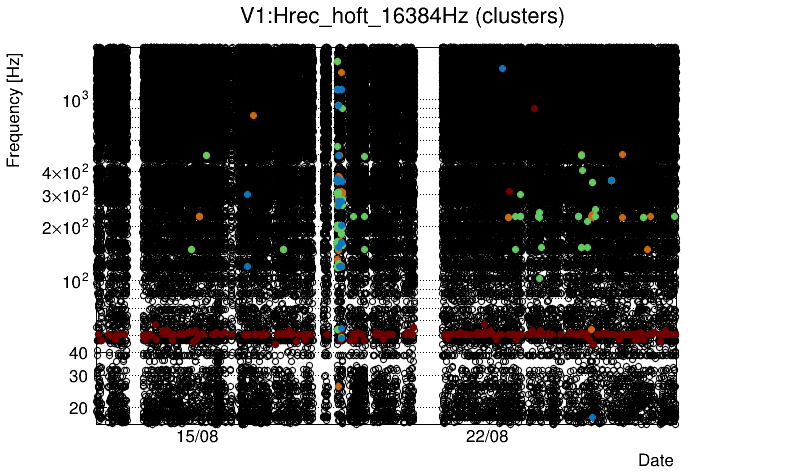

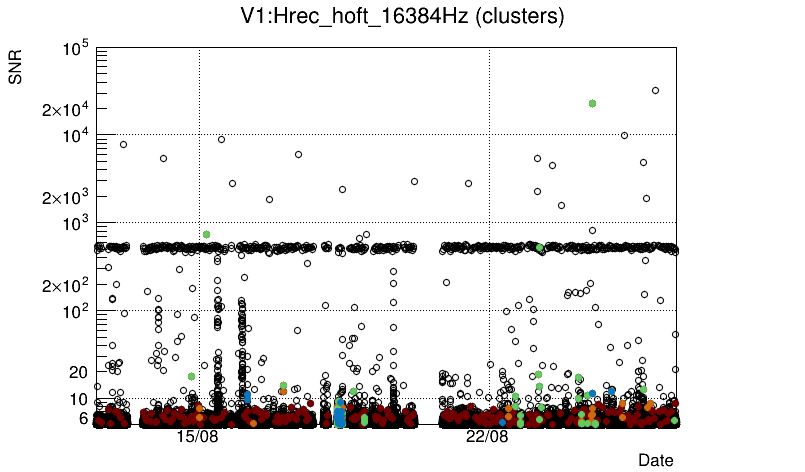

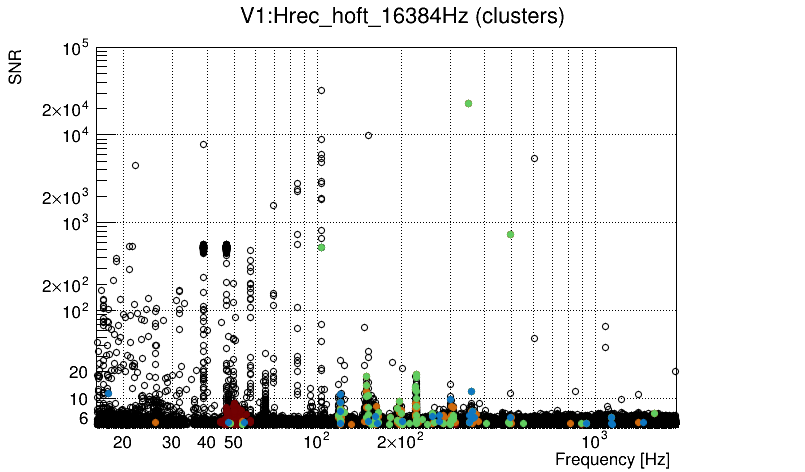

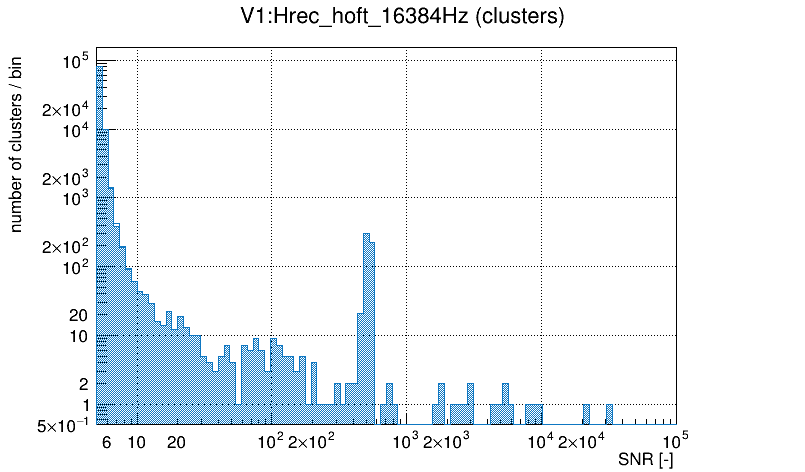

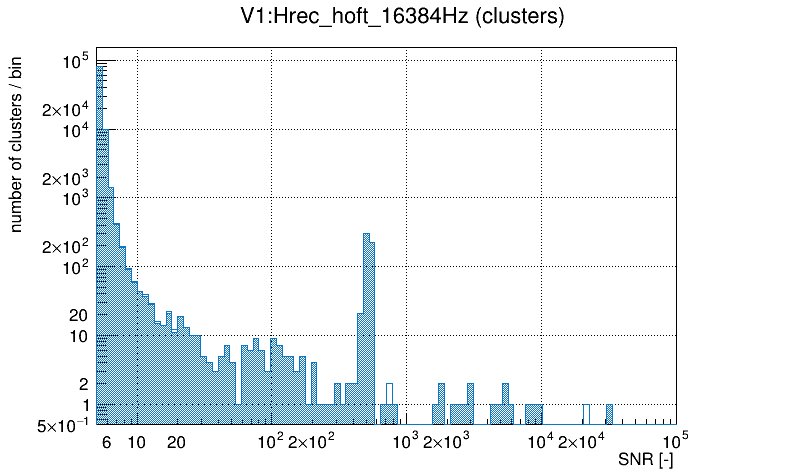

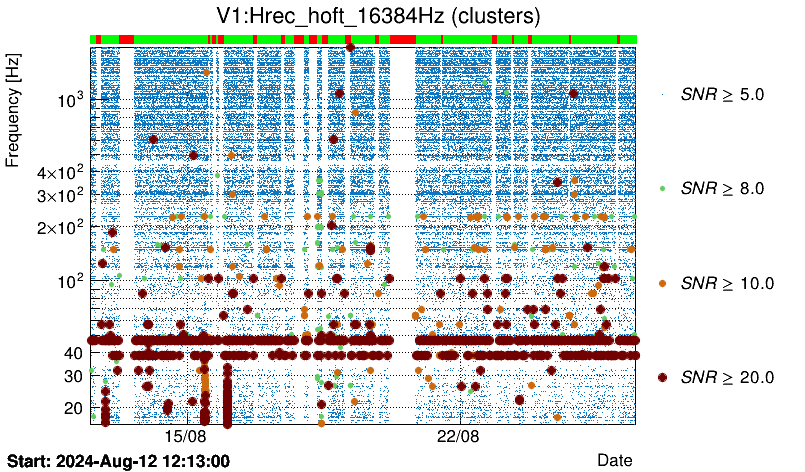

| V1:Hrec_hoft_16384Hz: 94622 clusters |

|---|

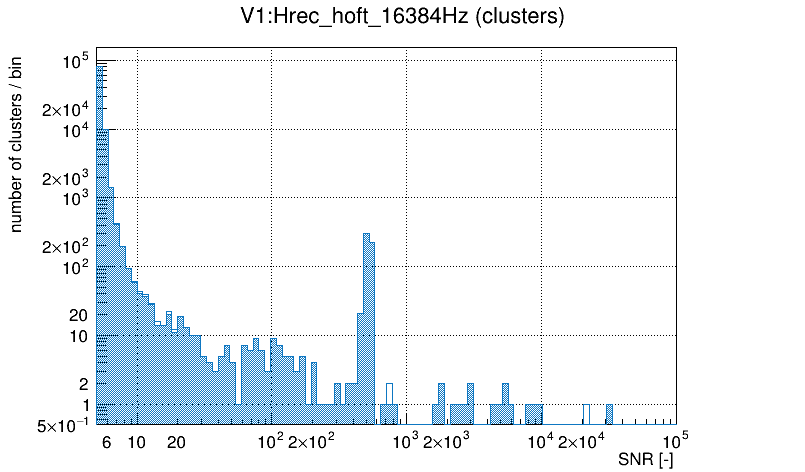

| V0 → V1:ASC_B2_QD1_H_0, vetoed clusters: 194 (0.205 %) |

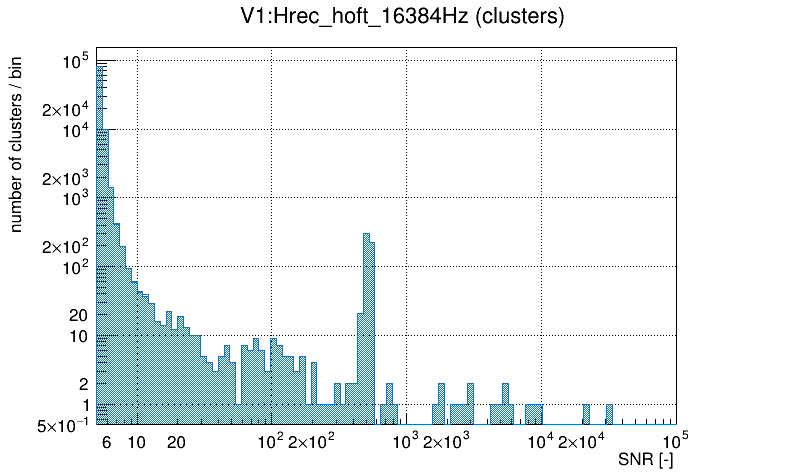

| V1 → V1:ASC_B1p_QD1_H_0, vetoed clusters: 100 (0.106 %) |

| V2 → V1:ASC_B1p_QD2_H_0, vetoed clusters: 77 (0.081 %) |

| V3 → V1:ASC_B1p_QD1_V_0, vetoed clusters: 27 (0.029 %) |