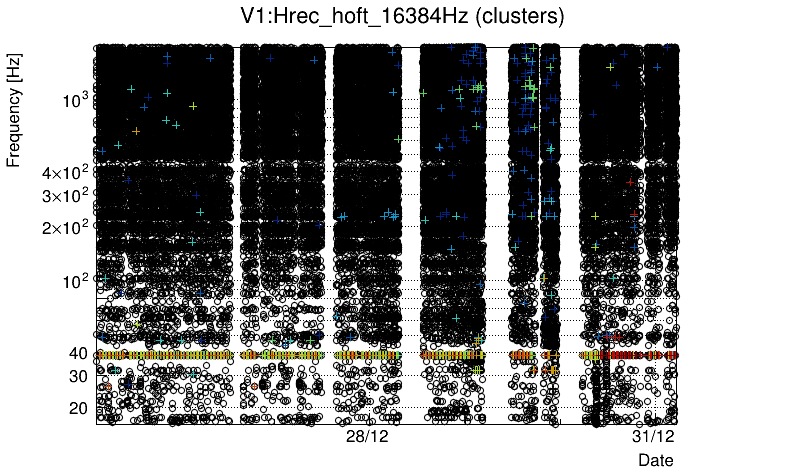

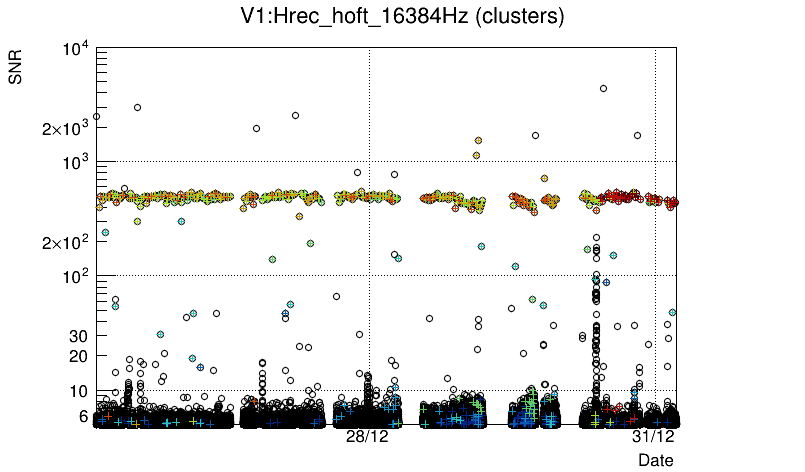

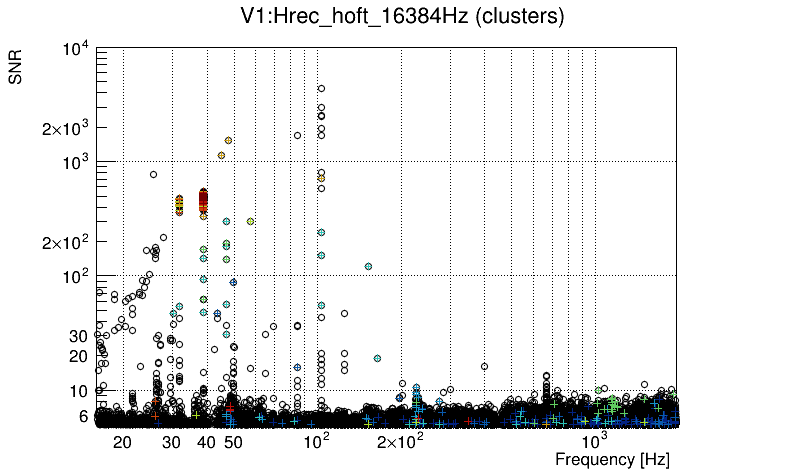

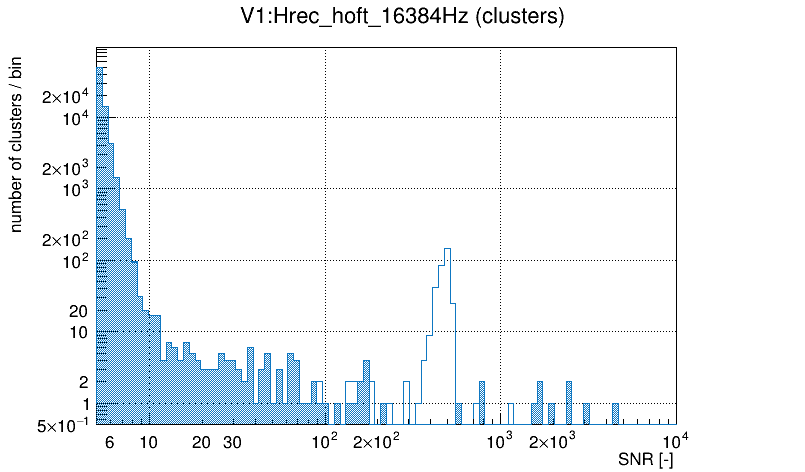

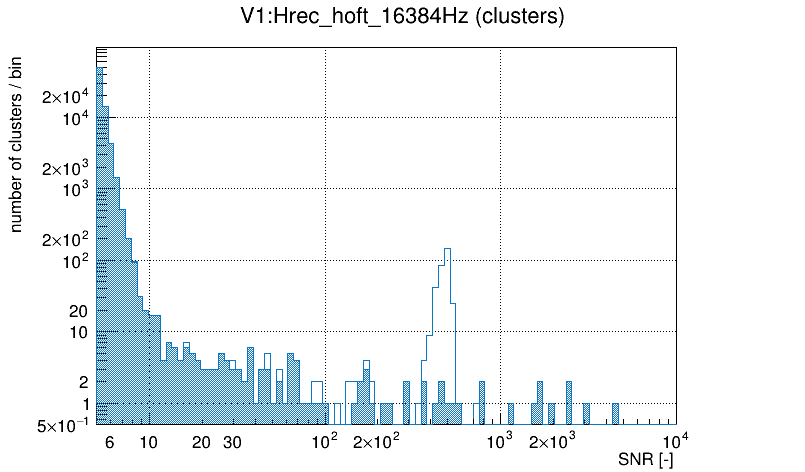

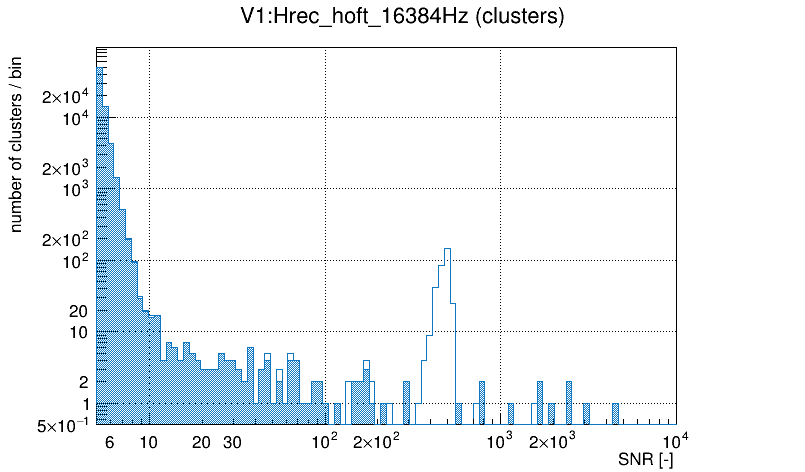

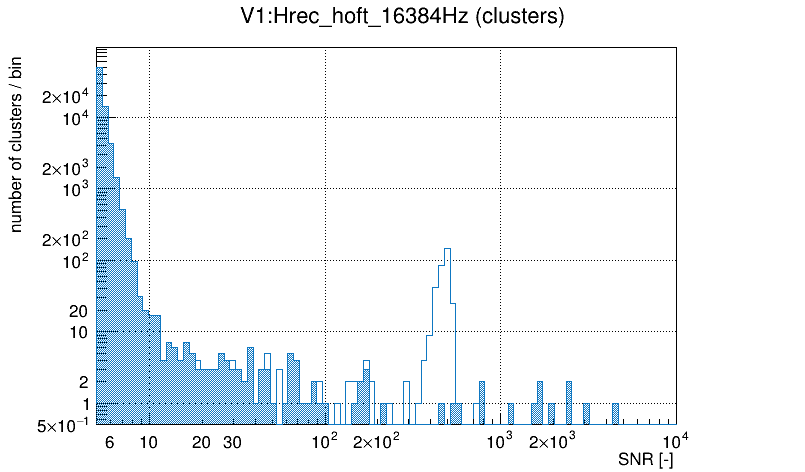

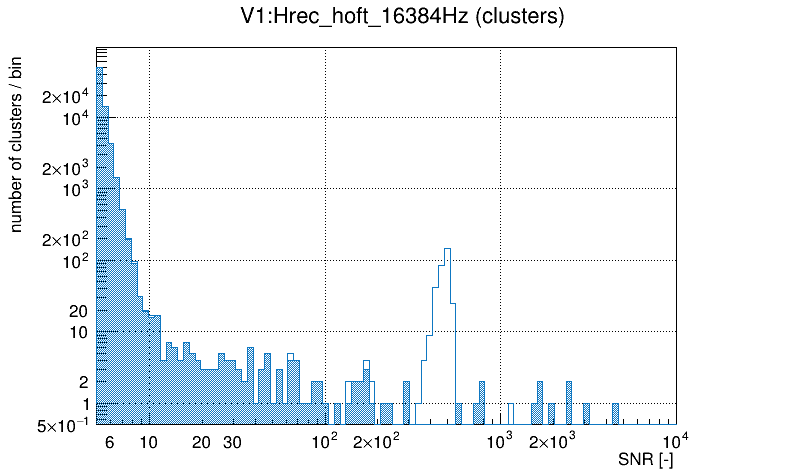

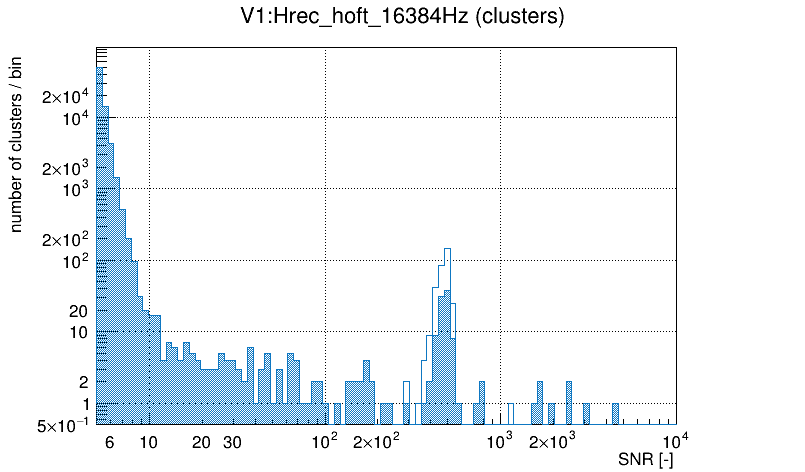

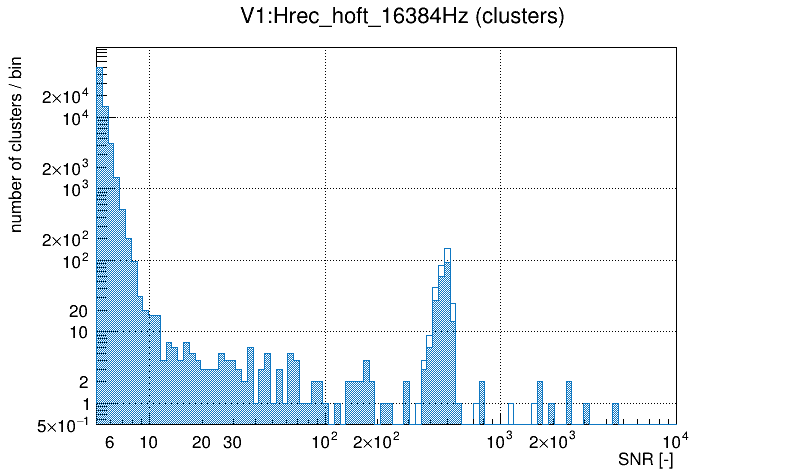

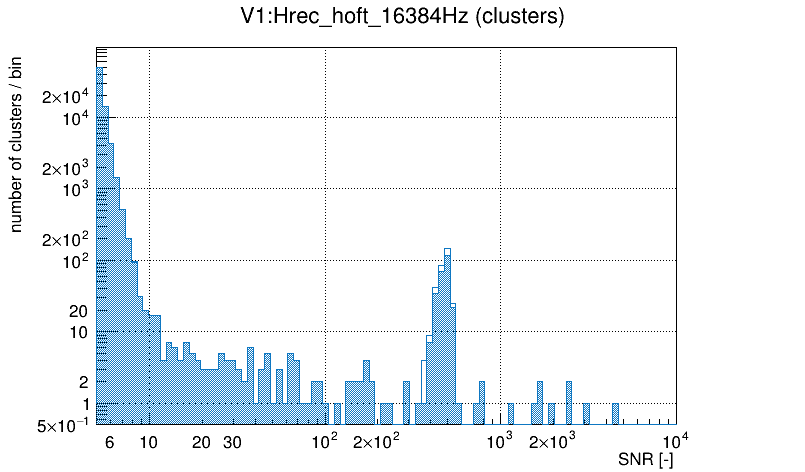

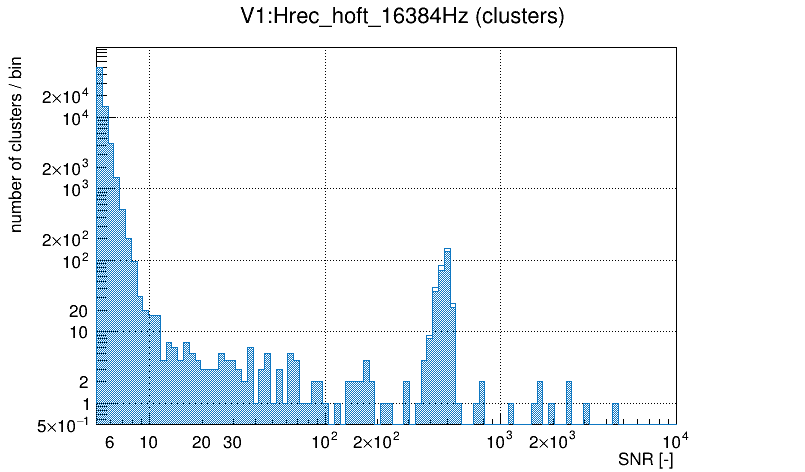

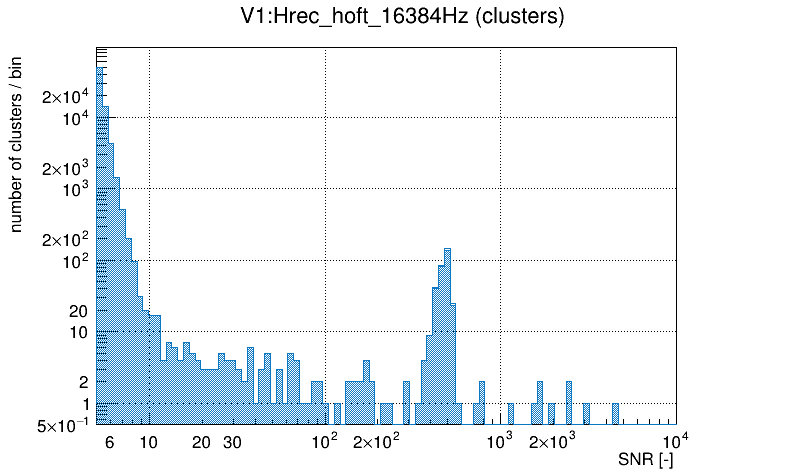

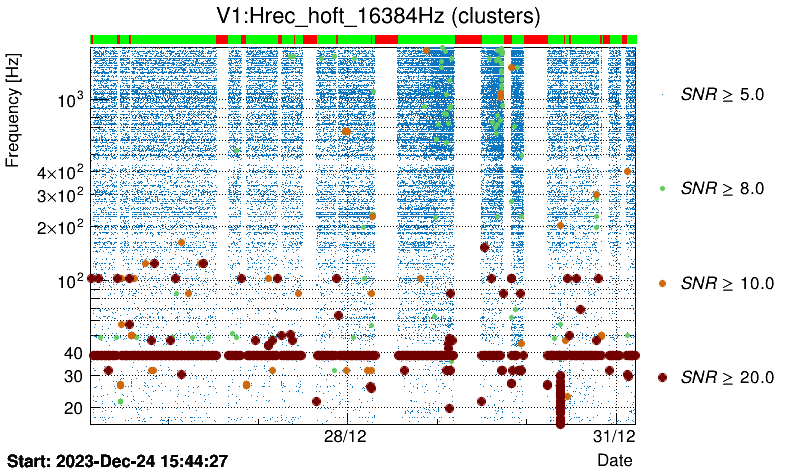

| V1:Hrec_hoft_16384Hz: 71452 clusters |

|---|

| V0 → V1:Sc_WI_FF50HZ_GAIN_0, vetoed clusters: 419 (0.586 %) |

| V1 → V1:Sc_WI_FF50HZ_P_ERR_0, vetoed clusters: 349 (0.488 %) |

| V2 → V1:Sc_WI_MAR_Z_CORR_0, vetoed clusters: 342 (0.479 %) |

| V3 → V1:Sc_WI_FF50HZ_PHASE_0, vetoed clusters: 340 (0.476 %) |

| V4 → V1:Sc_WI_MAR_Y_CORR_0, vetoed clusters: 338 (0.473 %) |

| V5 → V1:Sc_WI_MIR_X_AA_0, vetoed clusters: 228 (0.319 %) |

| V6 → V1:Sc_WI_MIR_VOUT_UR_0, vetoed clusters: 111 (0.155 %) |

| V7 → V1:Sc_WI_MIR_Y_AA_0, vetoed clusters: 60 (0.084 %) |

| V8 → V1:Sc_WI_FF50HZ_G_ERR_0, vetoed clusters: 39 (0.055 %) |

| V9 → V1:Sc_WI_MIR_VOUT_DL_0, vetoed clusters: 12 (0.017 %) |