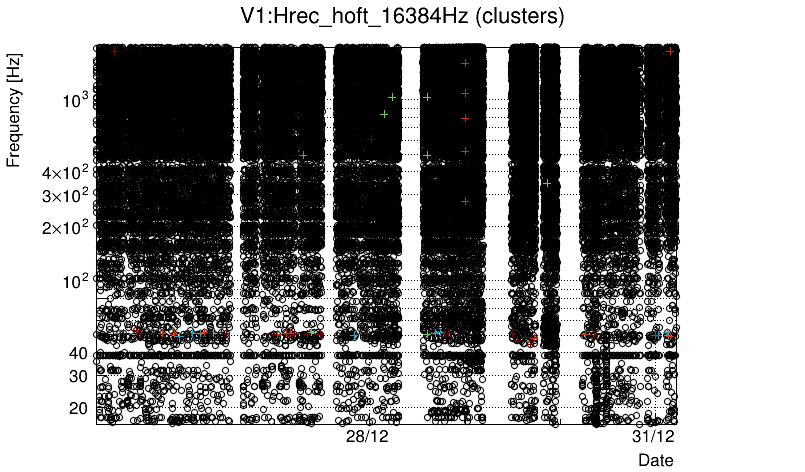

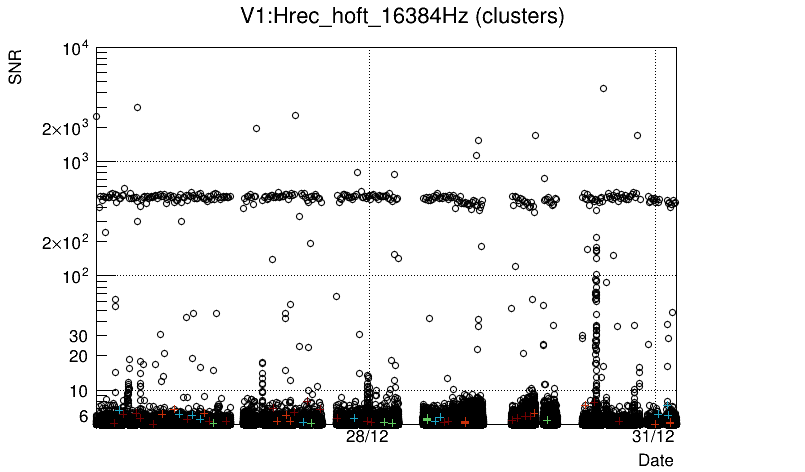

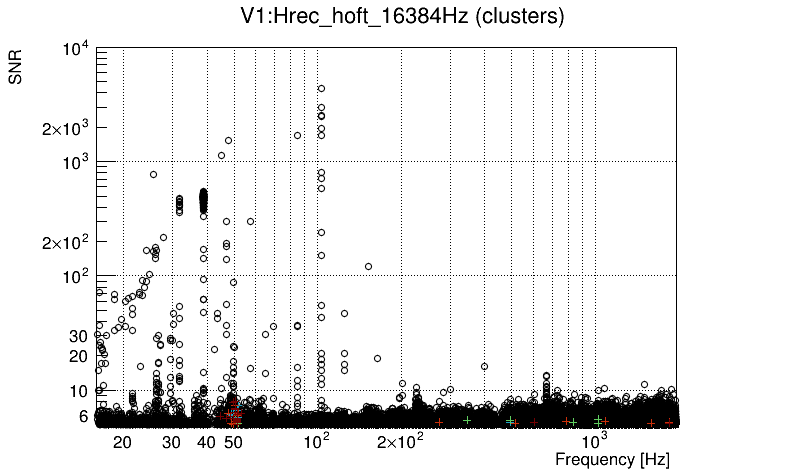

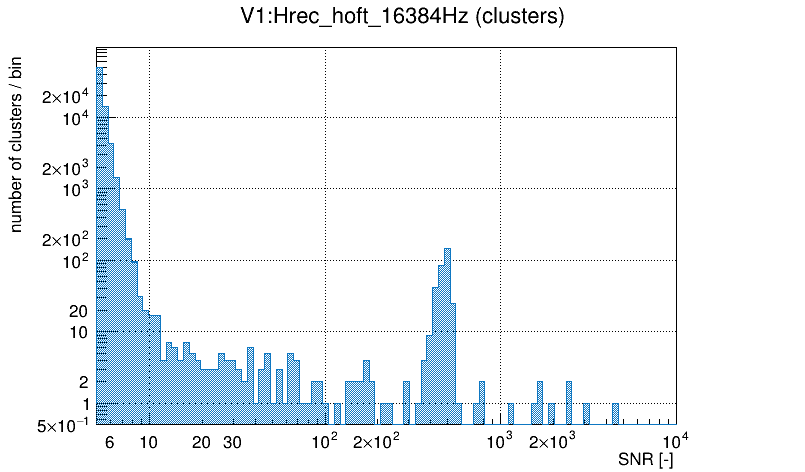

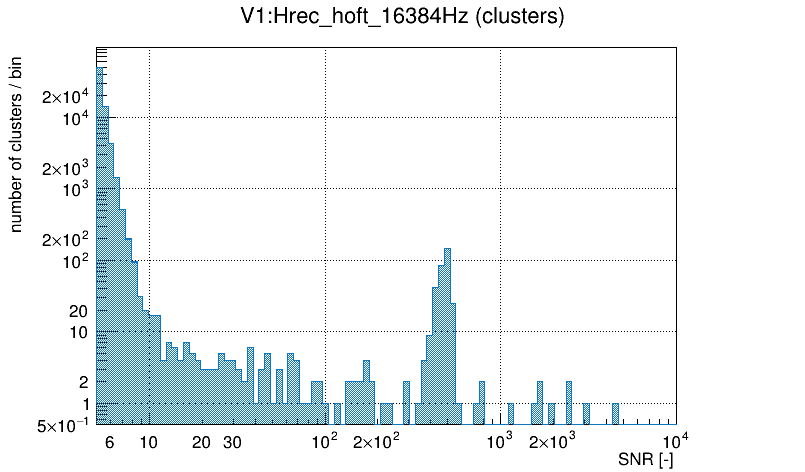

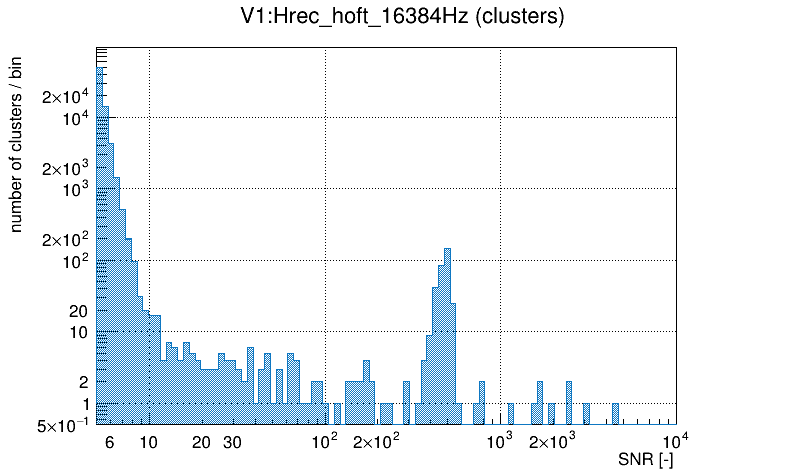

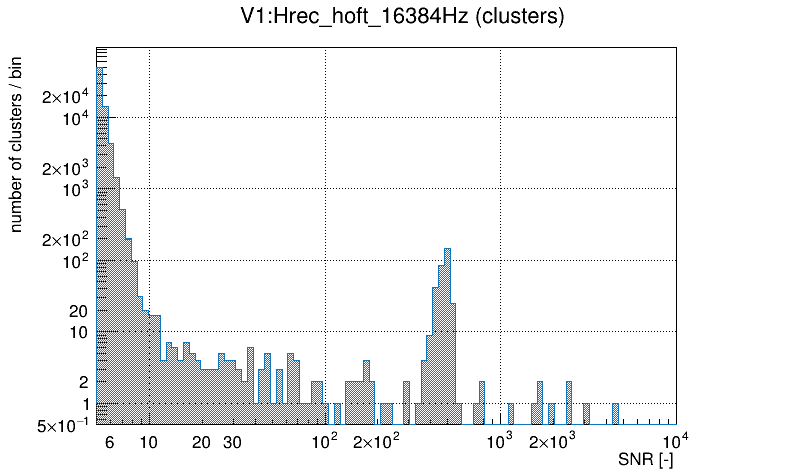

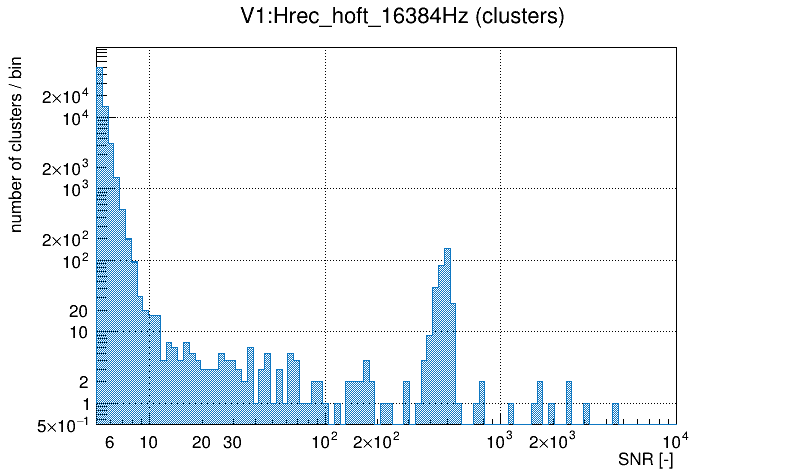

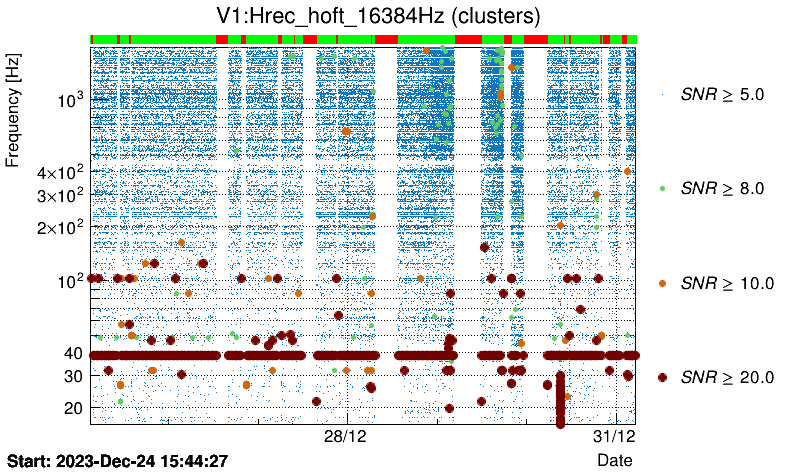

| V1:Hrec_hoft_16384Hz: 71452 clusters |

|---|

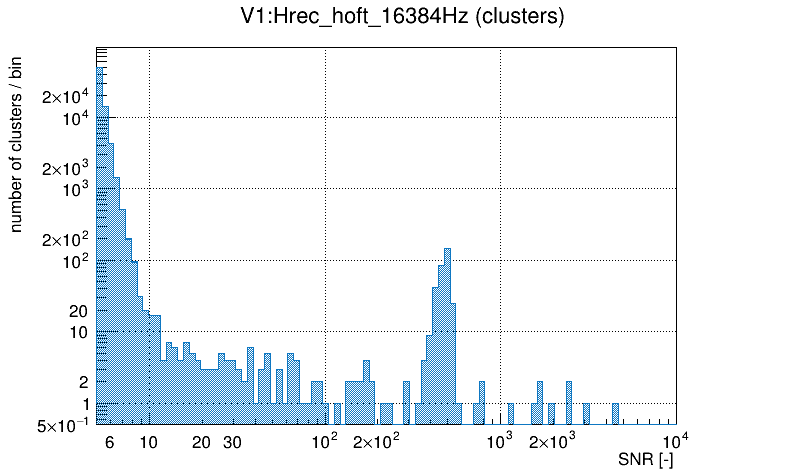

| V0 → V1:SSFS_Err_post_50kHz_0, vetoed clusters: 46 (0.064 %) |

| V1 → V1:SSFS_Err_pre_50kHz_0, vetoed clusters: 46 (0.064 %) |

| V2 → V1:SSFS_Err_I_unnorm_10kHz_0, vetoed clusters: 34 (0.048 %) |

| V3 → V1:SSFS_DigitalNoise_10kHz_0, vetoed clusters: 25 (0.035 %) |

| V4 → V1:SSFS_DigitalNoise_corr_10kHz_0, vetoed clusters: 25 (0.035 %) |

| V5 → V1:SSFS_Corr_50kHz_0, vetoed clusters: 23 (0.032 %) |