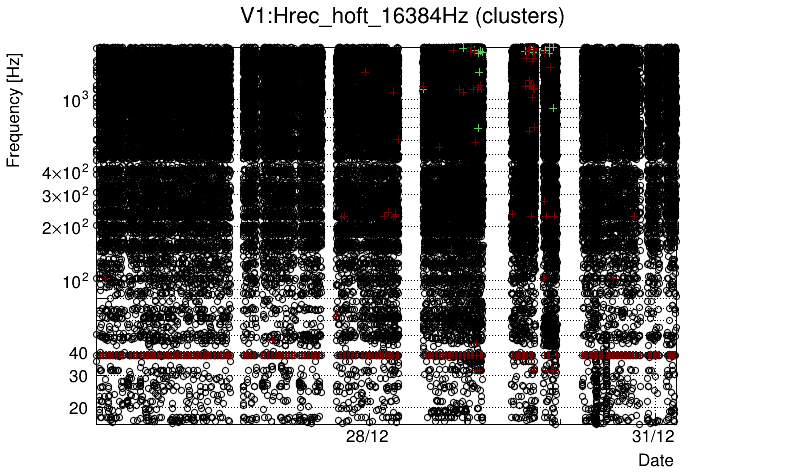

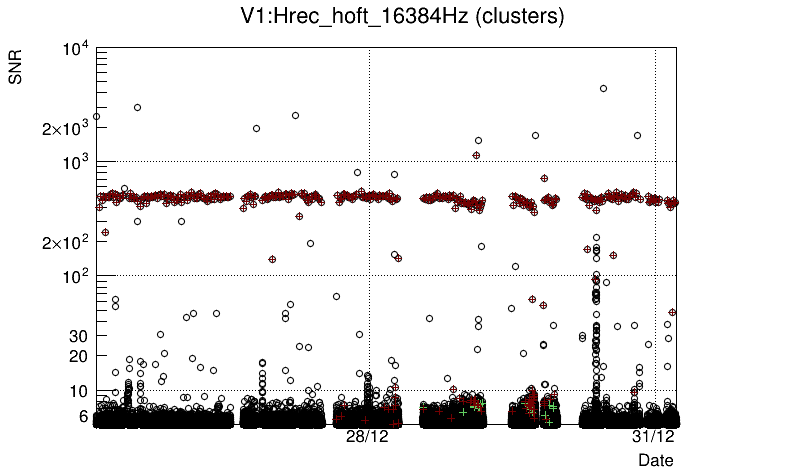

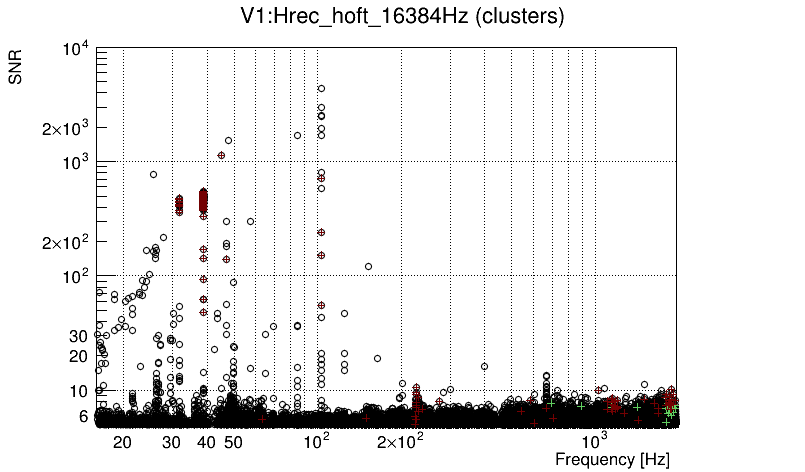

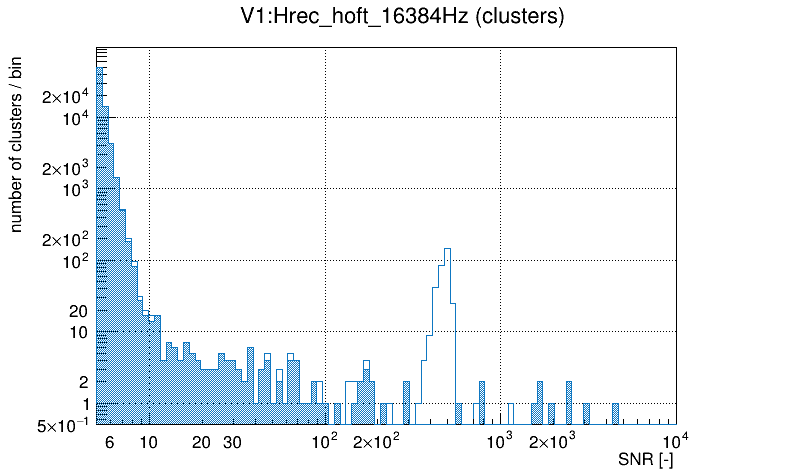

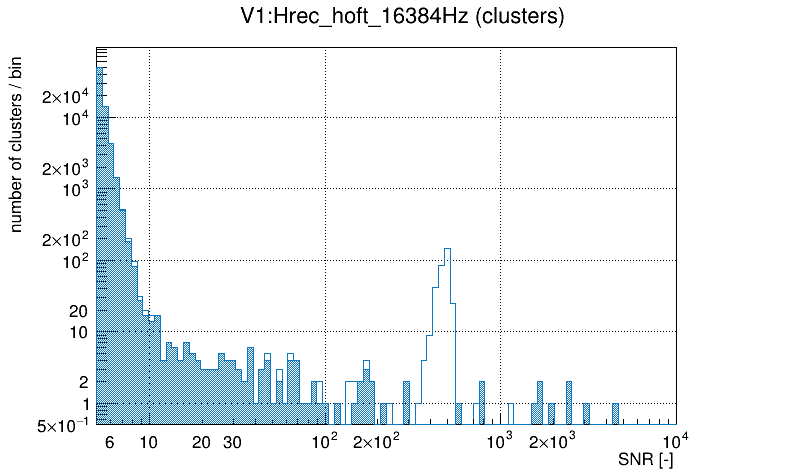

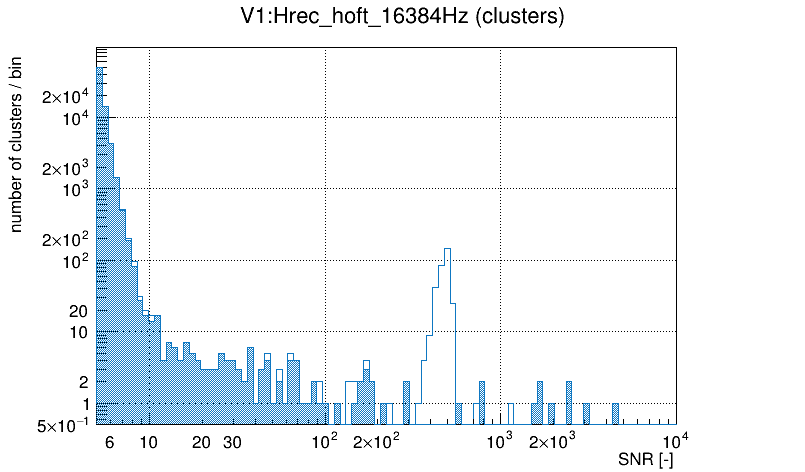

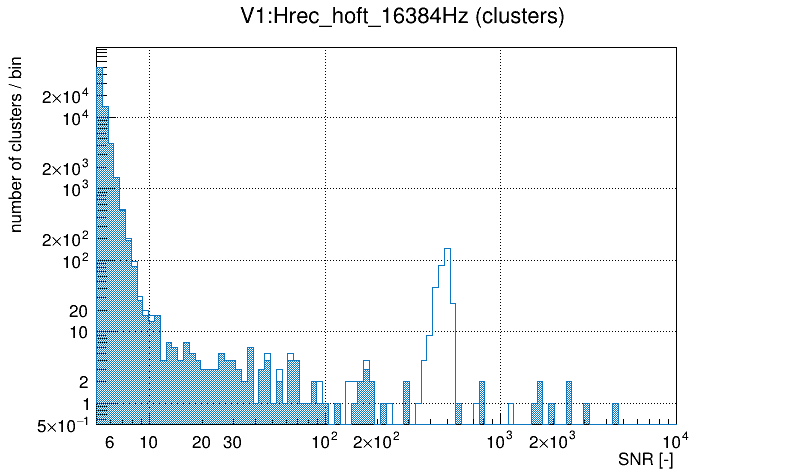

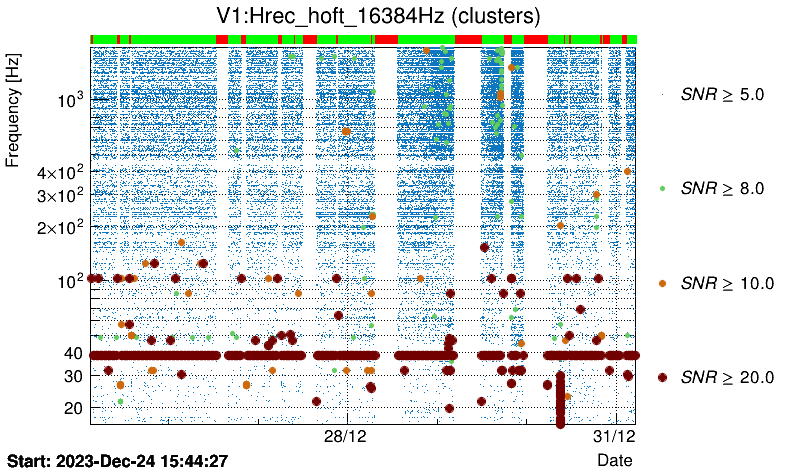

| V1:Hrec_hoft_16384Hz: 71452 clusters |

|---|

| V0 → V1:LSC_NE_CORR_0, vetoed clusters: 402 (0.563 %) |

| V1 → V1:LSC_NI_CORR_0, vetoed clusters: 402 (0.563 %) |

| V2 → V1:LSC_WI_CORR_0, vetoed clusters: 382 (0.535 %) |

| V3 → V1:LSC_WE_CORR_0, vetoed clusters: 382 (0.535 %) |