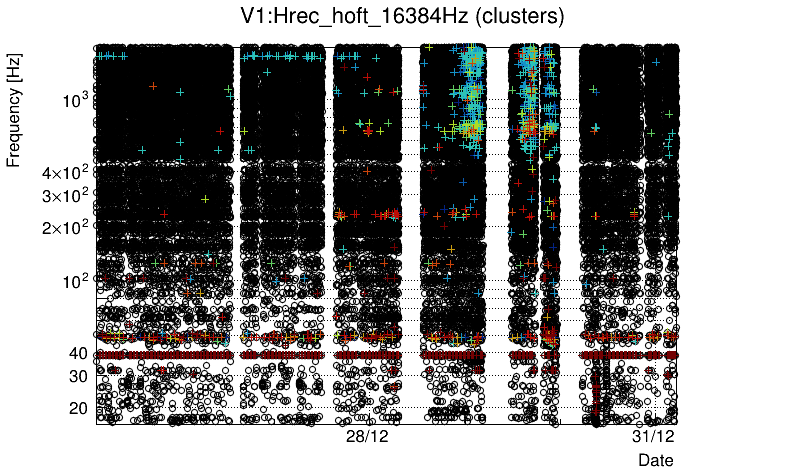

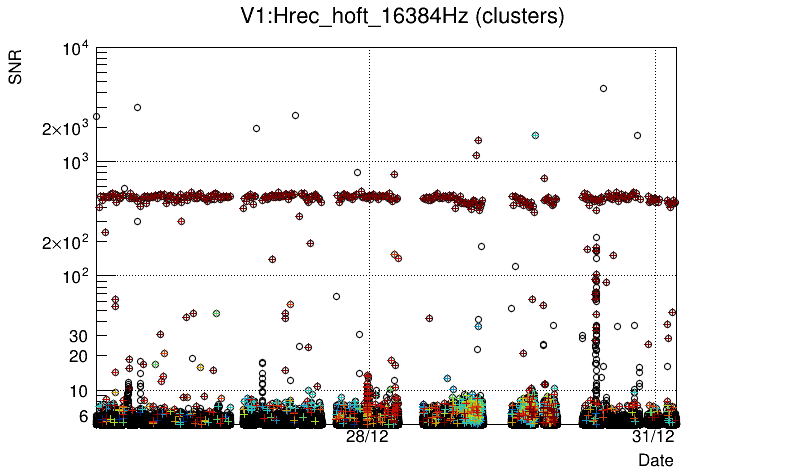

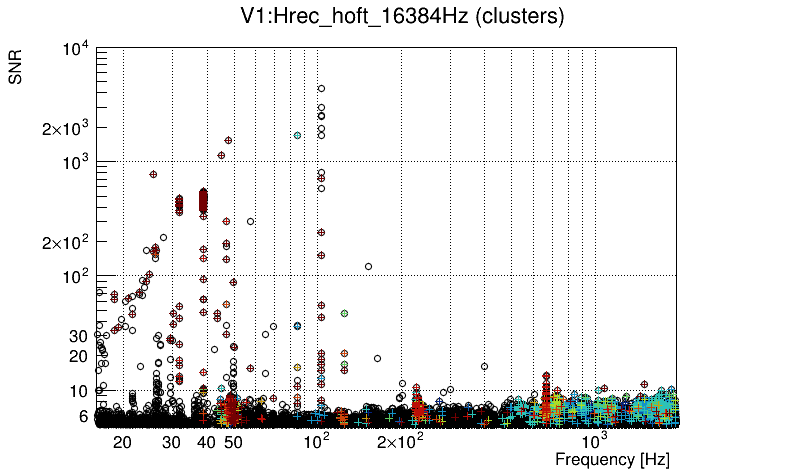

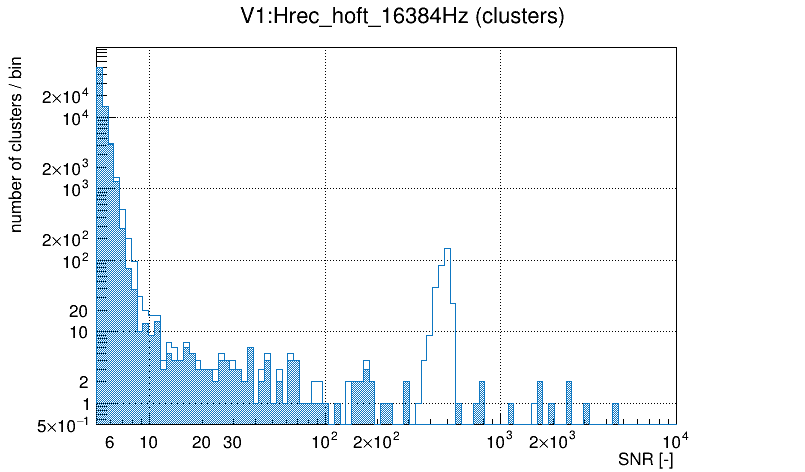

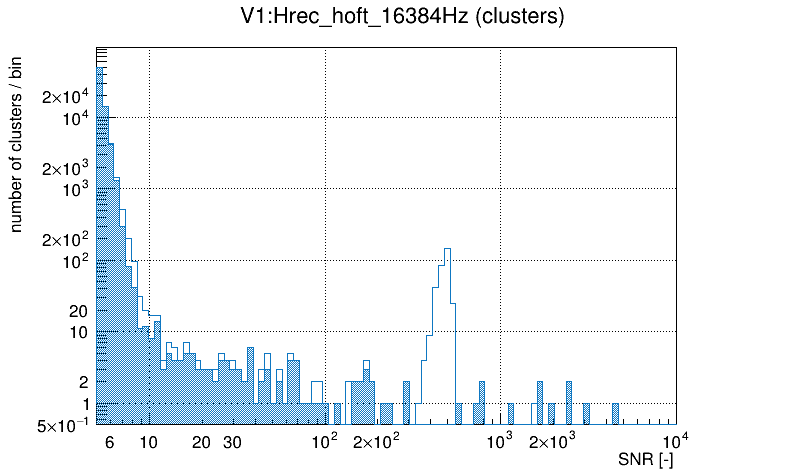

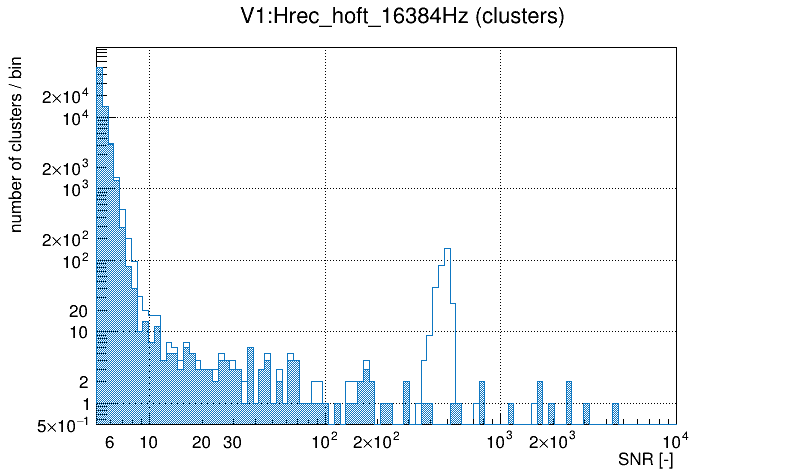

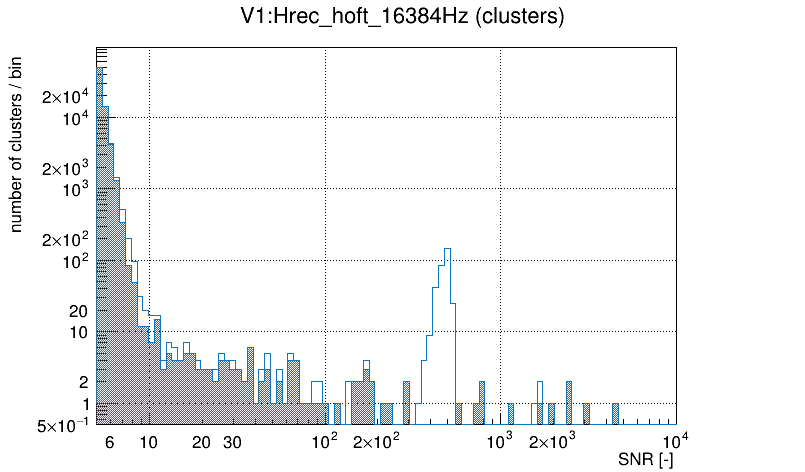

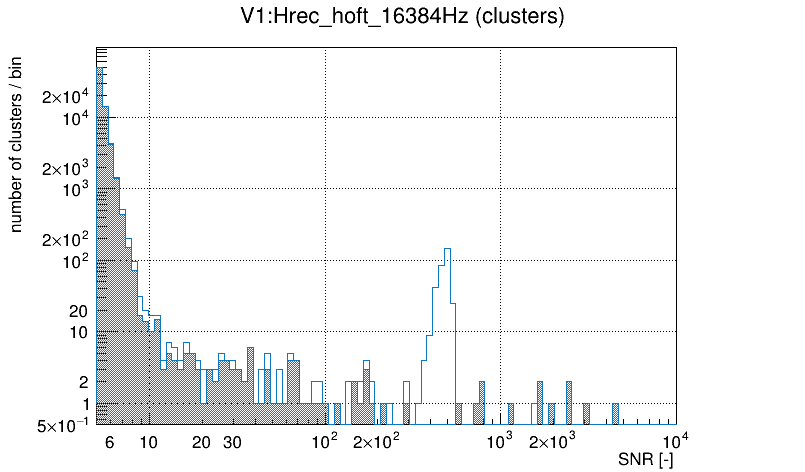

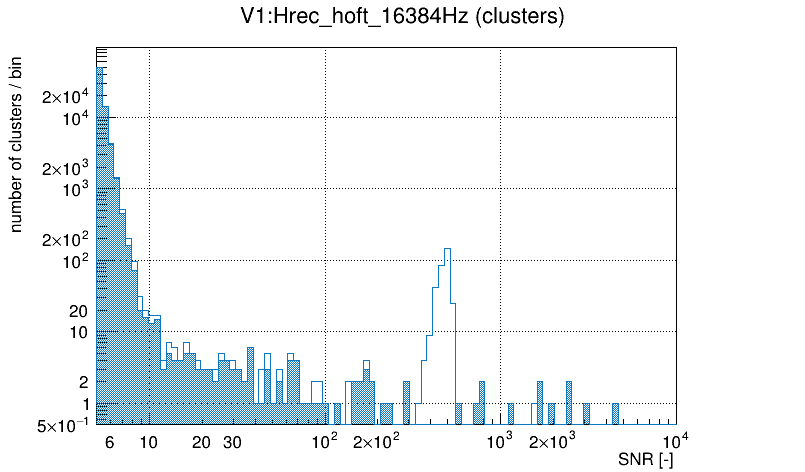

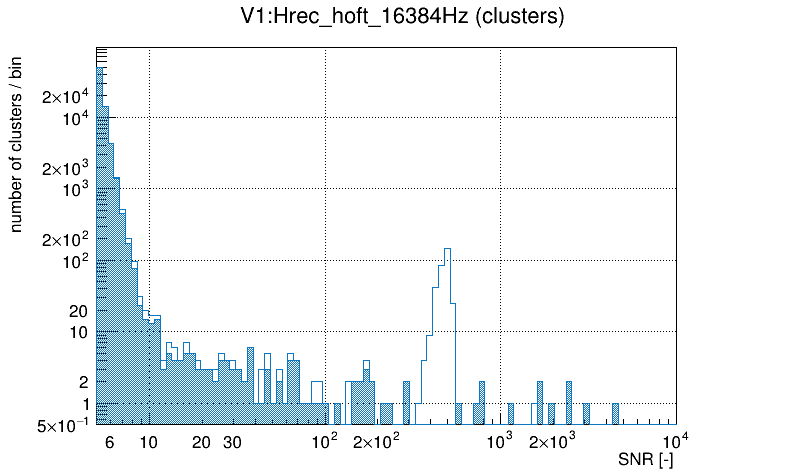

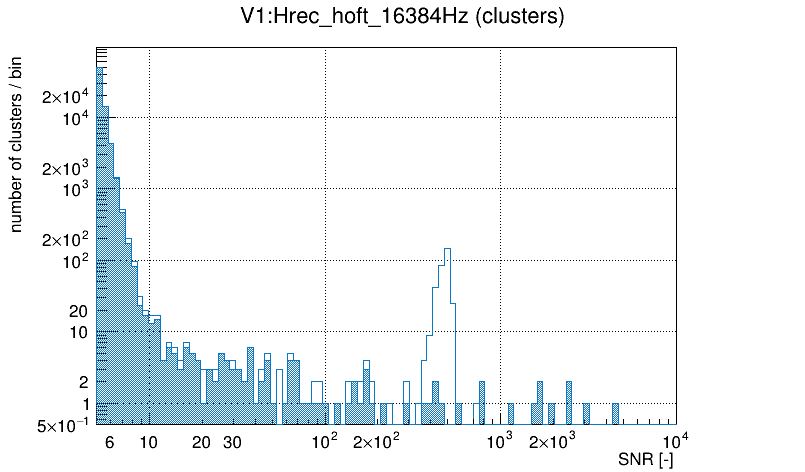

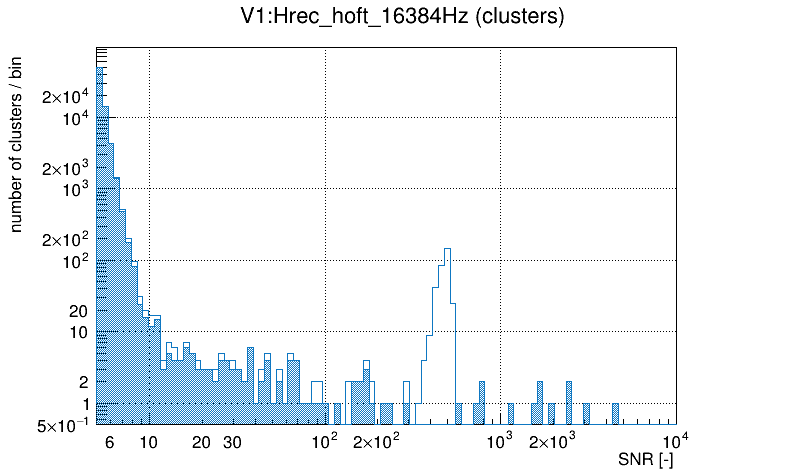

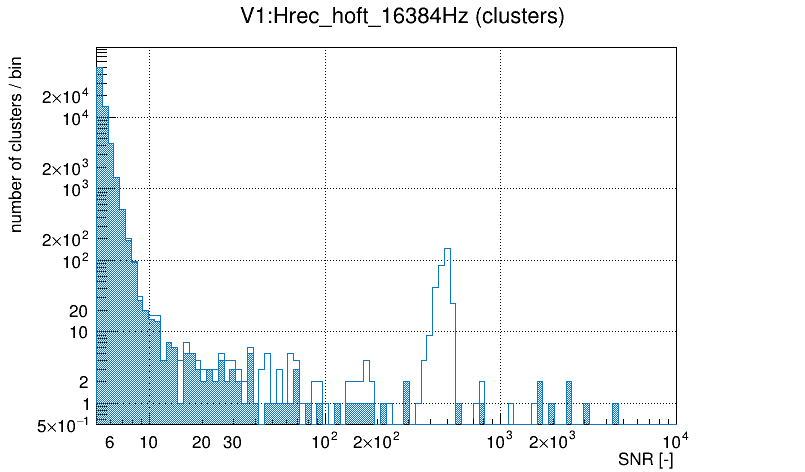

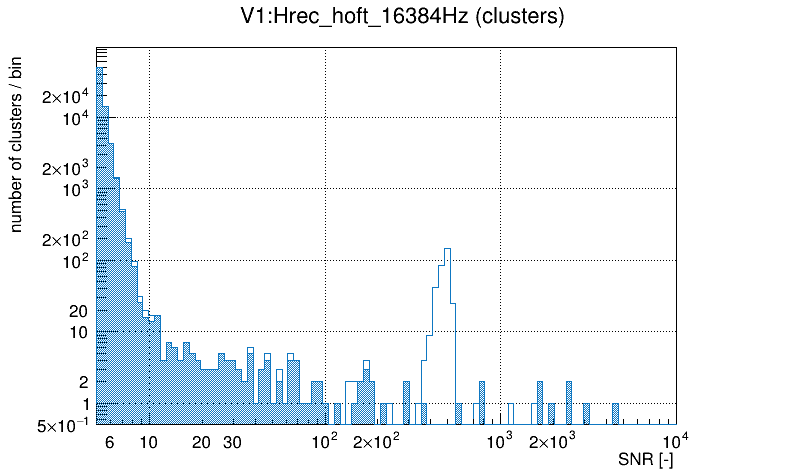

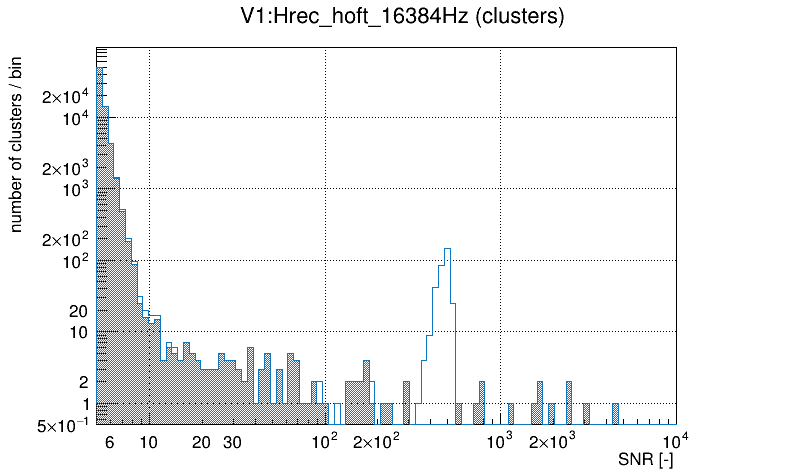

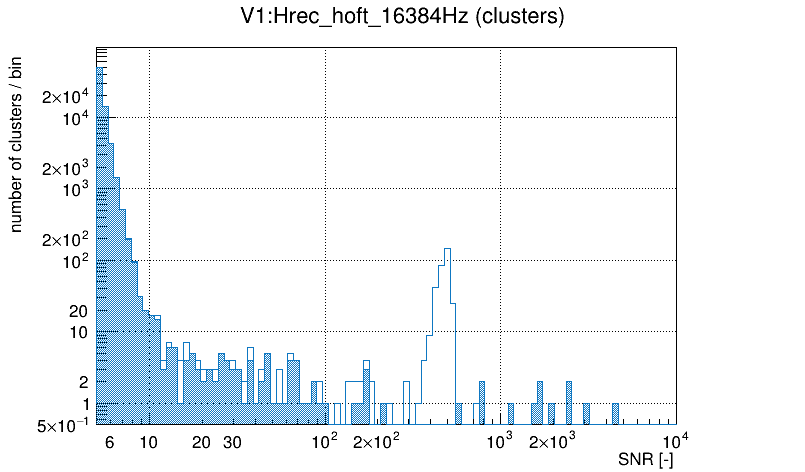

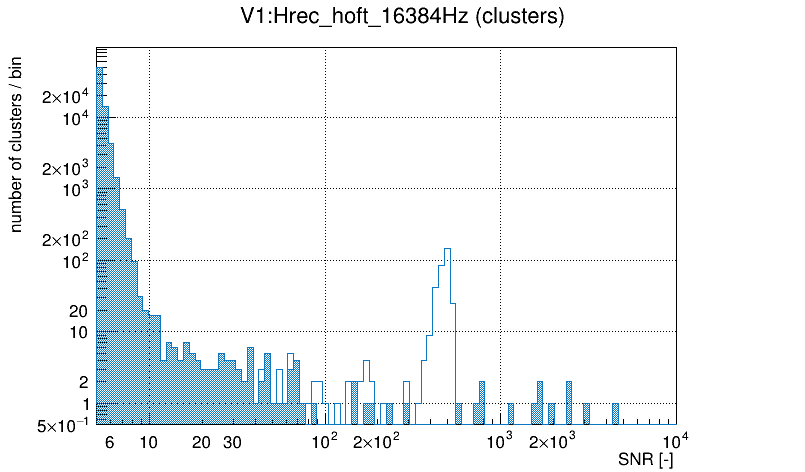

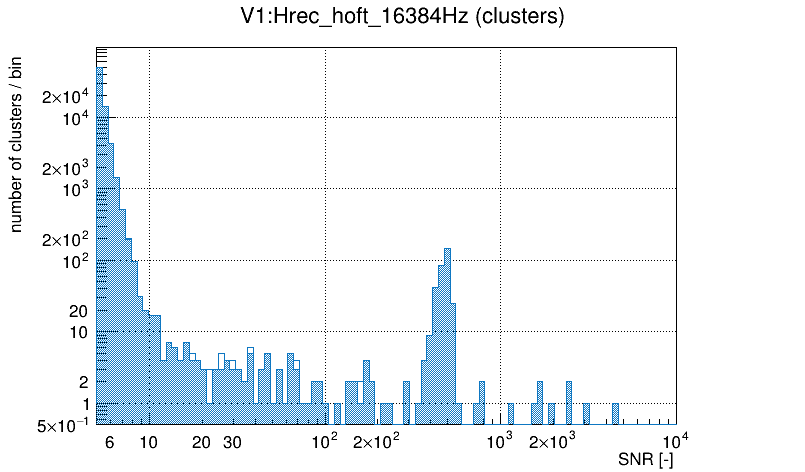

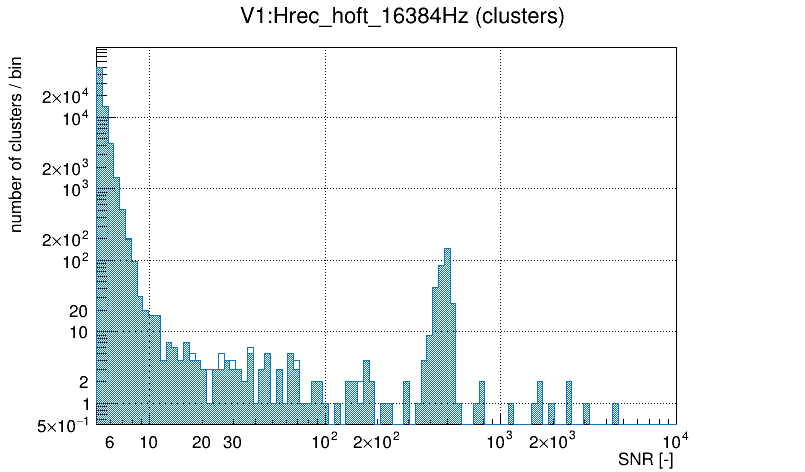

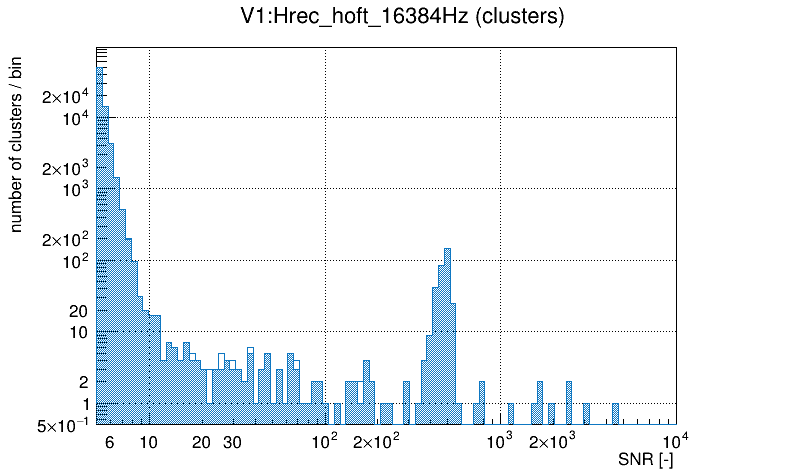

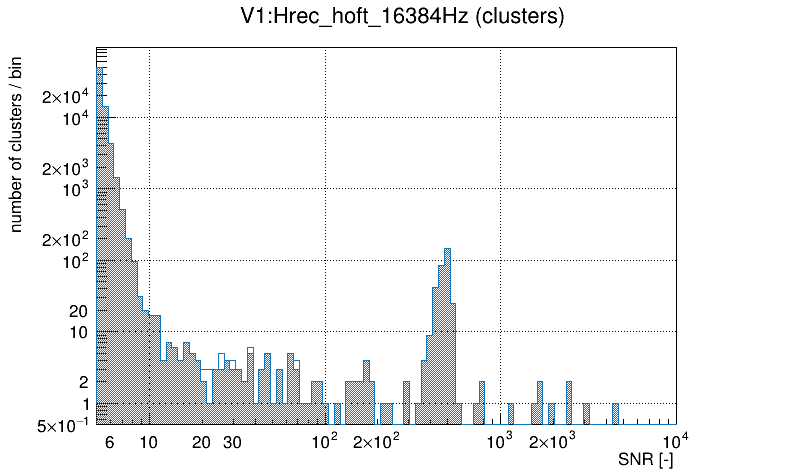

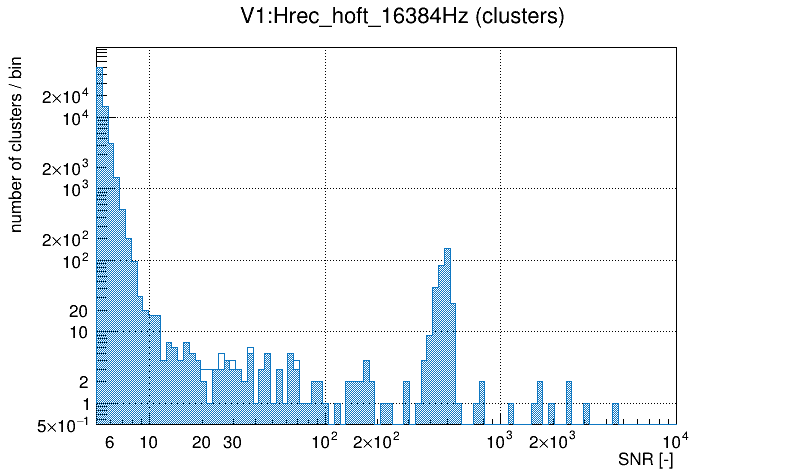

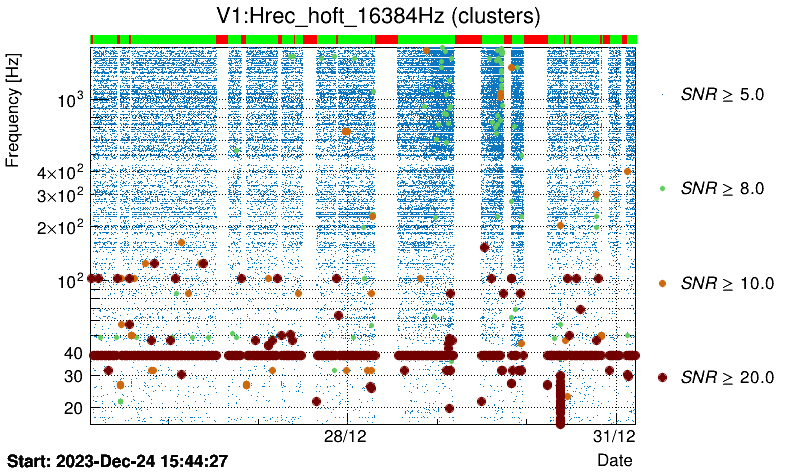

| V1:Hrec_hoft_16384Hz: 71452 clusters |

|---|

| V0 → V1:LSC_DARM_0, vetoed clusters: 1101 (1.541 %) |

| V1 → V1:LSC_DARM_ERR_0, vetoed clusters: 1066 (1.492 %) |

| V2 → V1:LSC_DARM_CORR_raw_0, vetoed clusters: 1014 (1.419 %) |

| V3 → V1:LSC_DARM_INPUT_0, vetoed clusters: 973 (1.362 %) |

| V4 → V1:LSC_DCP_DARM_CORR_FLT_LF_0, vetoed clusters: 660 (0.924 %) |

| V5 → V1:LSC_DCP_DARM_ERR_FLT_HF_0, vetoed clusters: 608 (0.851 %) |

| V6 → V1:LSC_DCP_DARM_ERR_FLT_HF_DEL_0, vetoed clusters: 561 (0.785 %) |

| V7 → V1:LSC_DCP_DARM_ERR_FLT_LF_0, vetoed clusters: 510 (0.714 %) |

| V8 → V1:LSC_DCP_DARM_ERR_FLT_LF_DEL_0, vetoed clusters: 484 (0.677 %) |

| V9 → V1:LSC_DCP_MM_RE_0, vetoed clusters: 430 (0.602 %) |