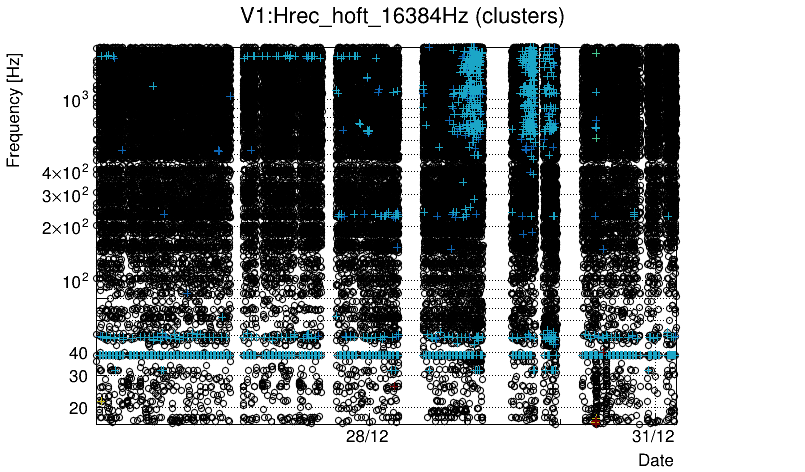

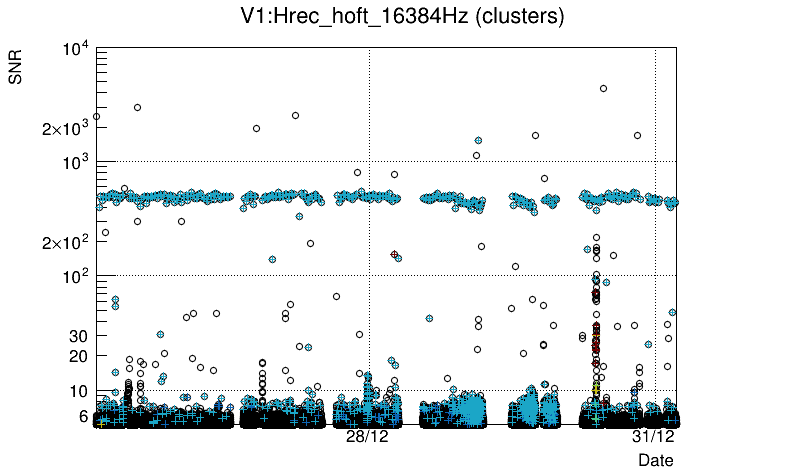

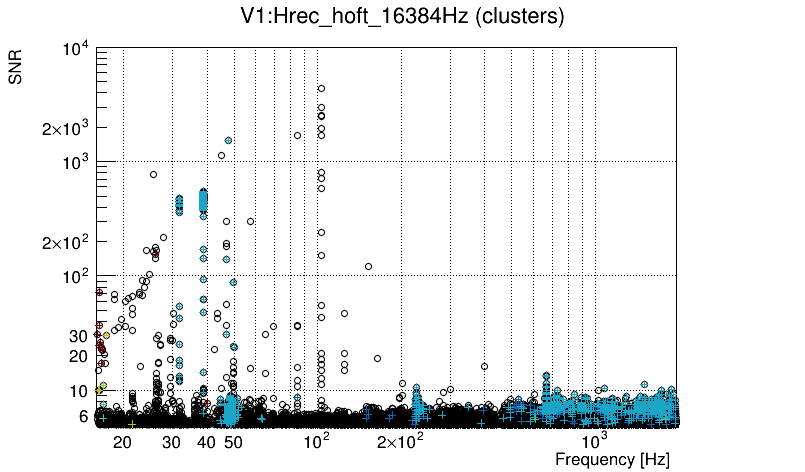

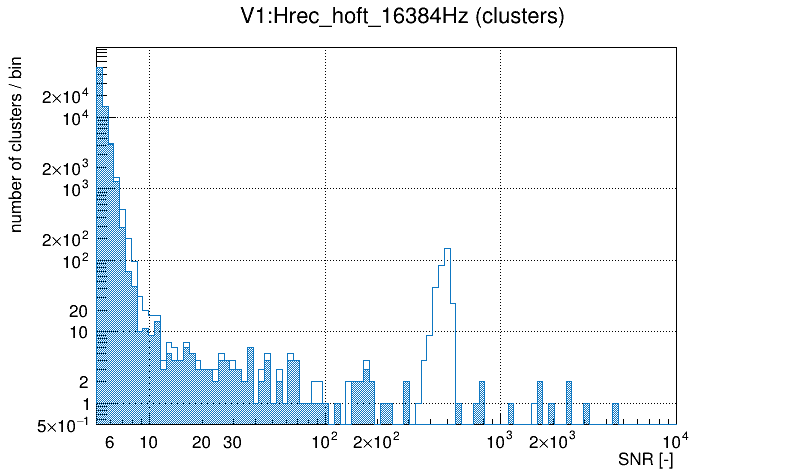

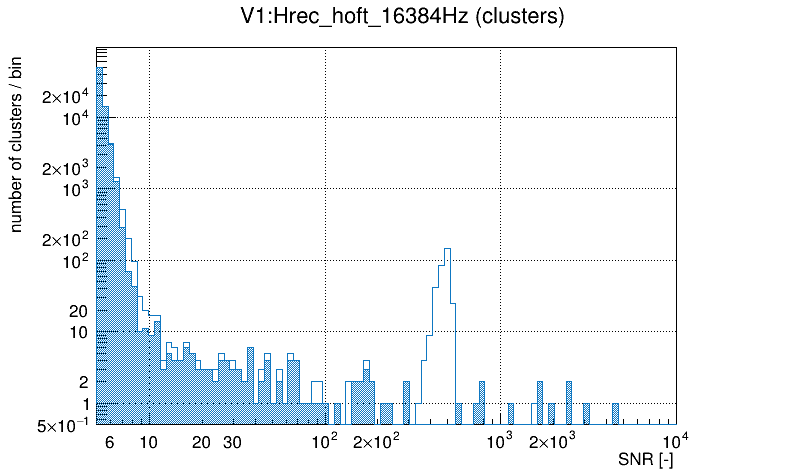

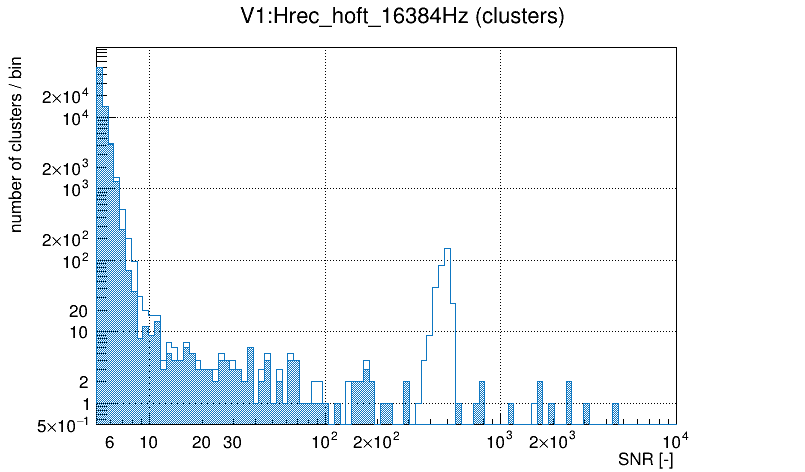

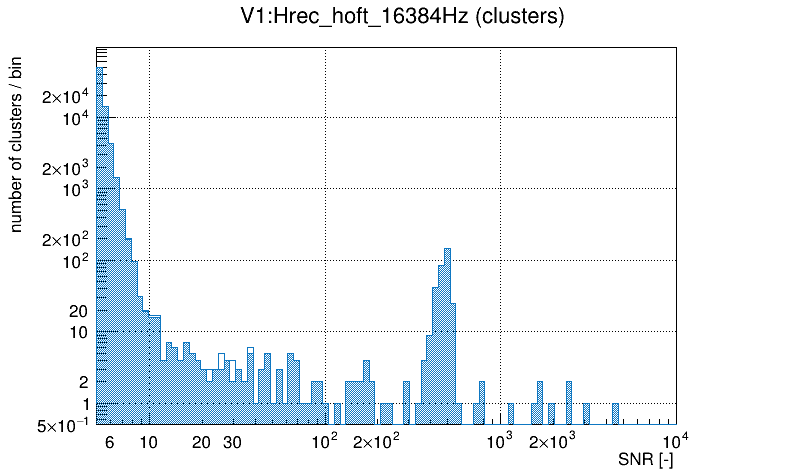

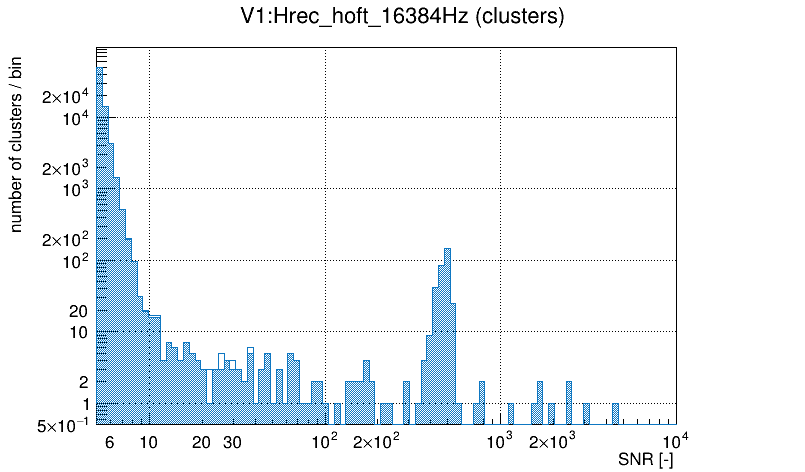

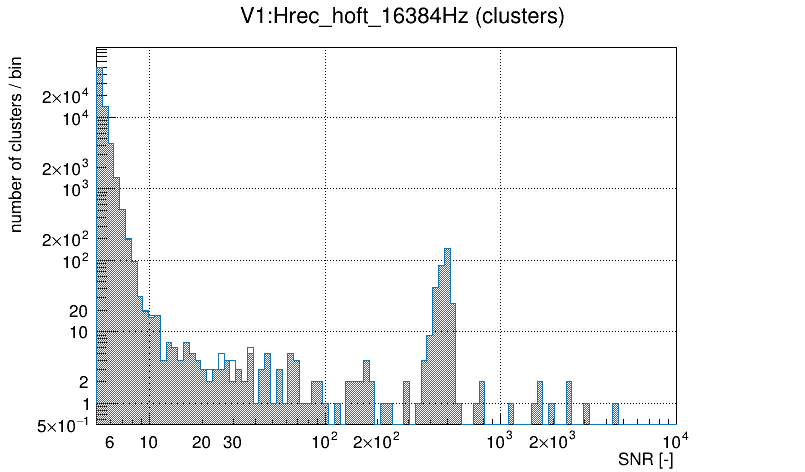

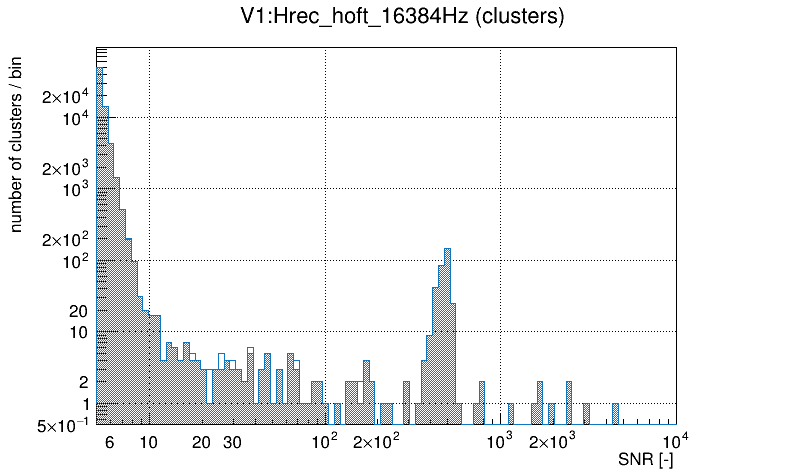

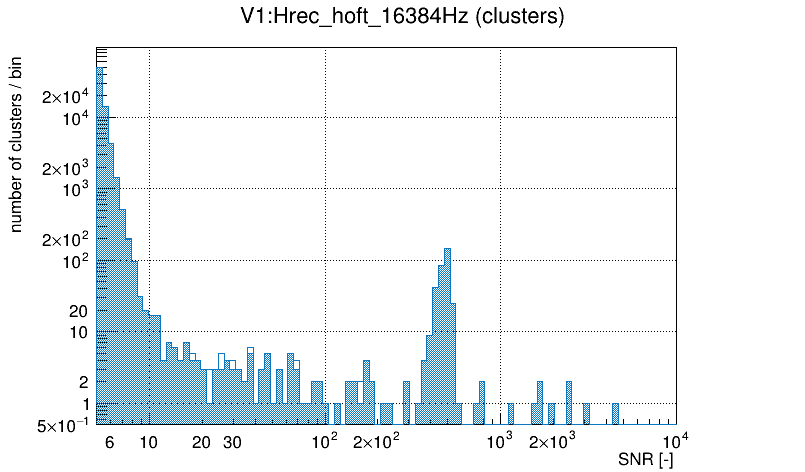

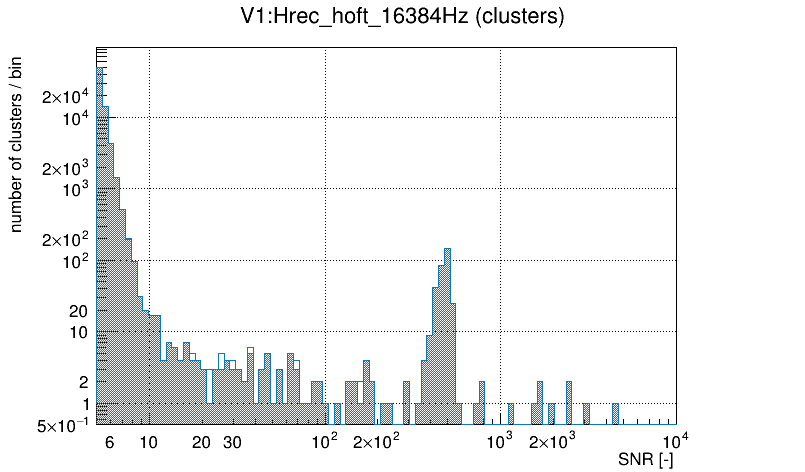

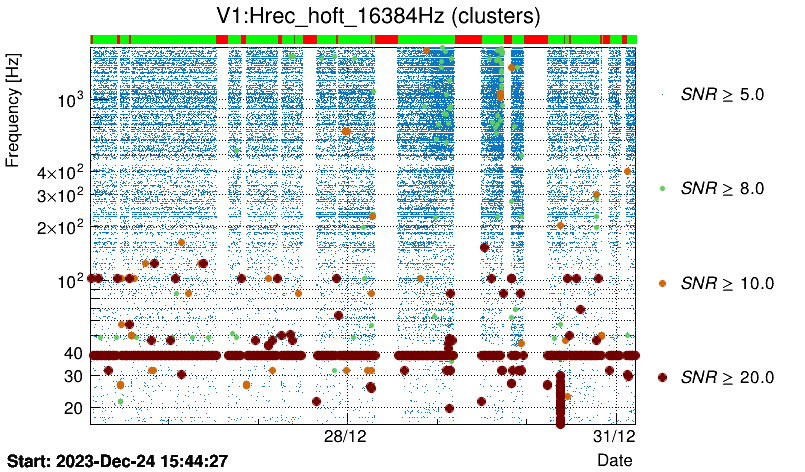

| V1:Hrec_hoft_16384Hz: 71452 clusters |

|---|

| V0 → V1:LSC_B1_DC_IN2_0, vetoed clusters: 1112 (1.556 %) |

| V1 → V1:LSC_B1_DC_INPUT_0, vetoed clusters: 1112 (1.556 %) |

| V2 → V1:LSC_B1_DC_IN1_0, vetoed clusters: 1105 (1.546 %) |

| V3 → V1:LSC_B2_6MHz_I_ARM_0, vetoed clusters: 15 (0.021 %) |

| V4 → V1:LSC_B1p_56MHz_I_ARM_NORM_0, vetoed clusters: 10 (0.014 %) |

| V5 → V1:LSC_B2_6MHz_I_ARM_NORM_0, vetoed clusters: 10 (0.014 %) |

| V6 → V1:LSC_B1B4_DIF_0, vetoed clusters: 10 (0.014 %) |

| V7 → V1:LSC_B2_DC_OLD_NORM_0, vetoed clusters: 10 (0.014 %) |

| V8 → V1:LSC_B1B4_SUM_0, vetoed clusters: 10 (0.014 %) |